R

Chapter 5: Using the Client-side GMII Data Path

10 Megabit per Second Frame Transmission

The operation of the core remains unchanged. It is the responsibility of the client logic (for example, an Ethernet MAC), to enter data at the correct rate. When operating at a speed of 10 Mbps, every byte of the MAC frame (from destination address to the frame check sequence field, inclusive) should each be repeated for 100 clock periods to achieve the desired bit rate. It is also the responsibility of the client logic to ensure that the interframe gap period is legal for the current speed of operation.

GMII Reception

1 Gigabit per Second Frame Reception

The timing of normal inbound frame transfer is illustrated in Figure

userclk2

gmii_rxd[7:0]preamble

gmii_rx_dv

gmii_rx_er

SFD D0 | D1 |

FCS

Figure 5-12: GMII Frame Reception at 1 Gbps

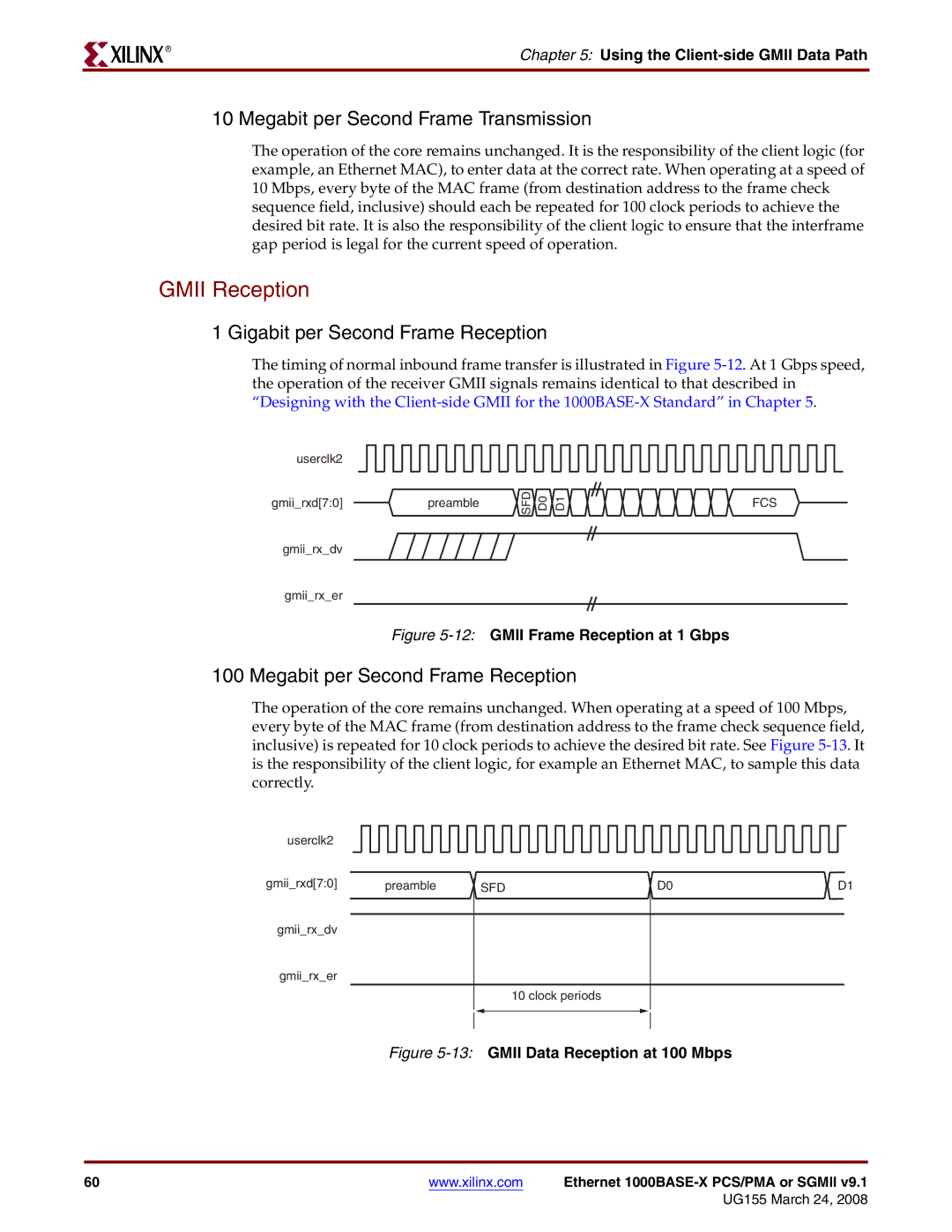

100 Megabit per Second Frame Reception

The operation of the core remains unchanged. When operating at a speed of 100 Mbps, every byte of the MAC frame (from destination address to the frame check sequence field, inclusive) is repeated for 10 clock periods to achieve the desired bit rate. See Figure

userclk2

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

preamble | SFD | D0 | D1 |

|

| 10 clock periods |

|

Figure |

| ||

60 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |