R

Chapter 12: Constraining the Core

All the constraints described in the section

With the MGT Rx Elastic Buffer bypassed, rxrecclk1 is provided by the MGT to the FPGA fabric for the recovered receiver data signals leaving the transceiver. This data is then written into the replacement Rx Elastic Buffer implemented in the FPGA fabric. See

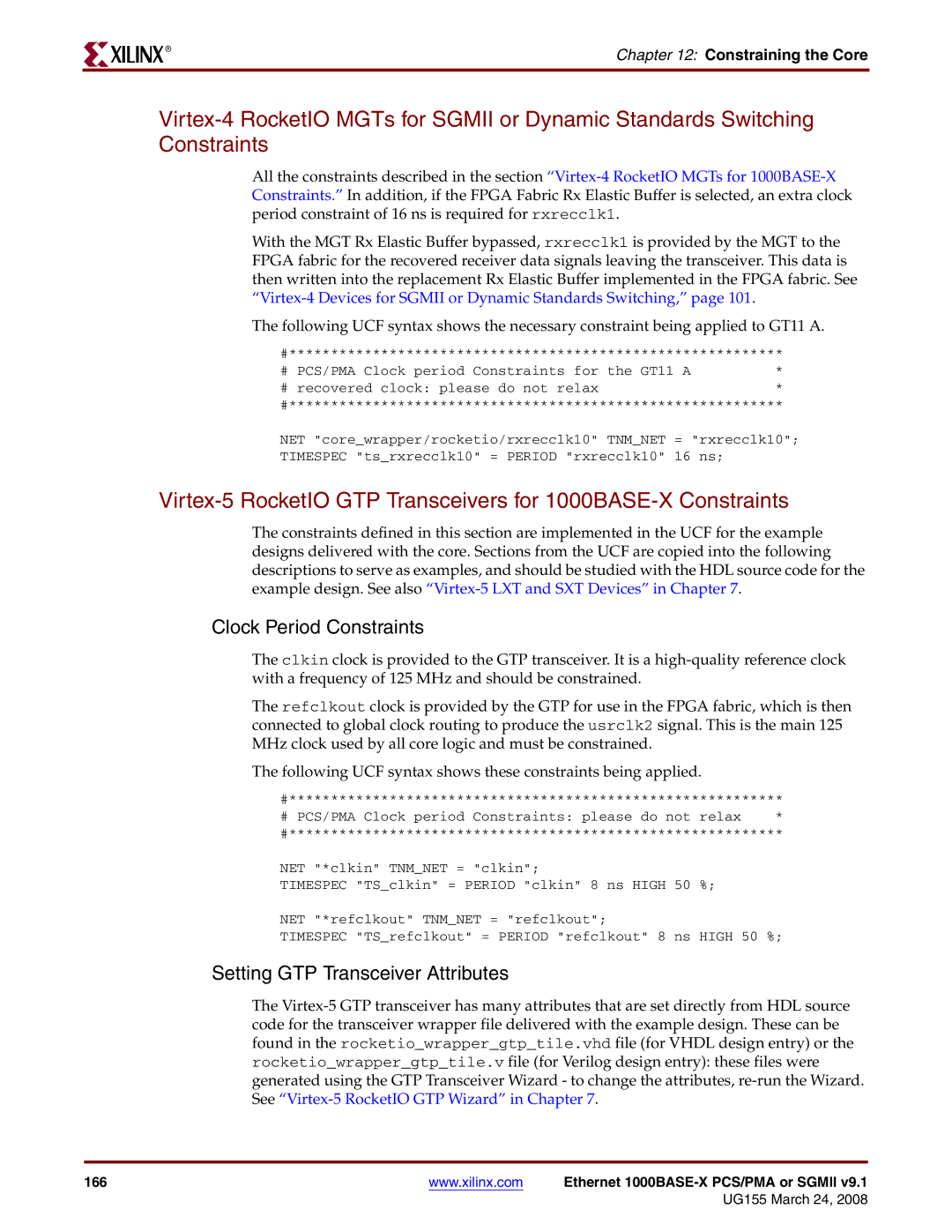

The following UCF syntax shows the necessary constraint being applied to GT11 A.

#***********************************************************

# | PCS/PMA Clock period Constraints for | the GT11 A | * |

# | recovered clock: please do not relax |

| * |

#***********************************************************

NET "core_wrapper/rocketio/rxrecclk10" TNM_NET = "rxrecclk10";

TIMESPEC "ts_rxrecclk10" = PERIOD "rxrecclk10" 16 ns;

The constraints defined in this section are implemented in the UCF for the example designs delivered with the core. Sections from the UCF are copied into the following descriptions to serve as examples, and should be studied with the HDL source code for the example design. See also

Clock Period Constraints

The clkin clock is provided to the GTP transceiver. It is a

The refclkout clock is provided by the GTP for use in the FPGA fabric, which is then connected to global clock routing to produce the usrclk2 signal. This is the main 125 MHz clock used by all core logic and must be constrained.

The following UCF syntax shows these constraints being applied.

#***********************************************************

# PCS/PMA Clock period Constraints: please do not relax * #***********************************************************

NET "*clkin" TNM_NET = "clkin";

TIMESPEC "TS_clkin" = PERIOD "clkin" 8 ns HIGH 50 %;

NET "*refclkout" TNM_NET = "refclkout";

TIMESPEC "TS_refclkout" = PERIOD "refclkout" 8 ns HIGH 50 %;

Setting GTP Transceiver Attributes

The

166 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |