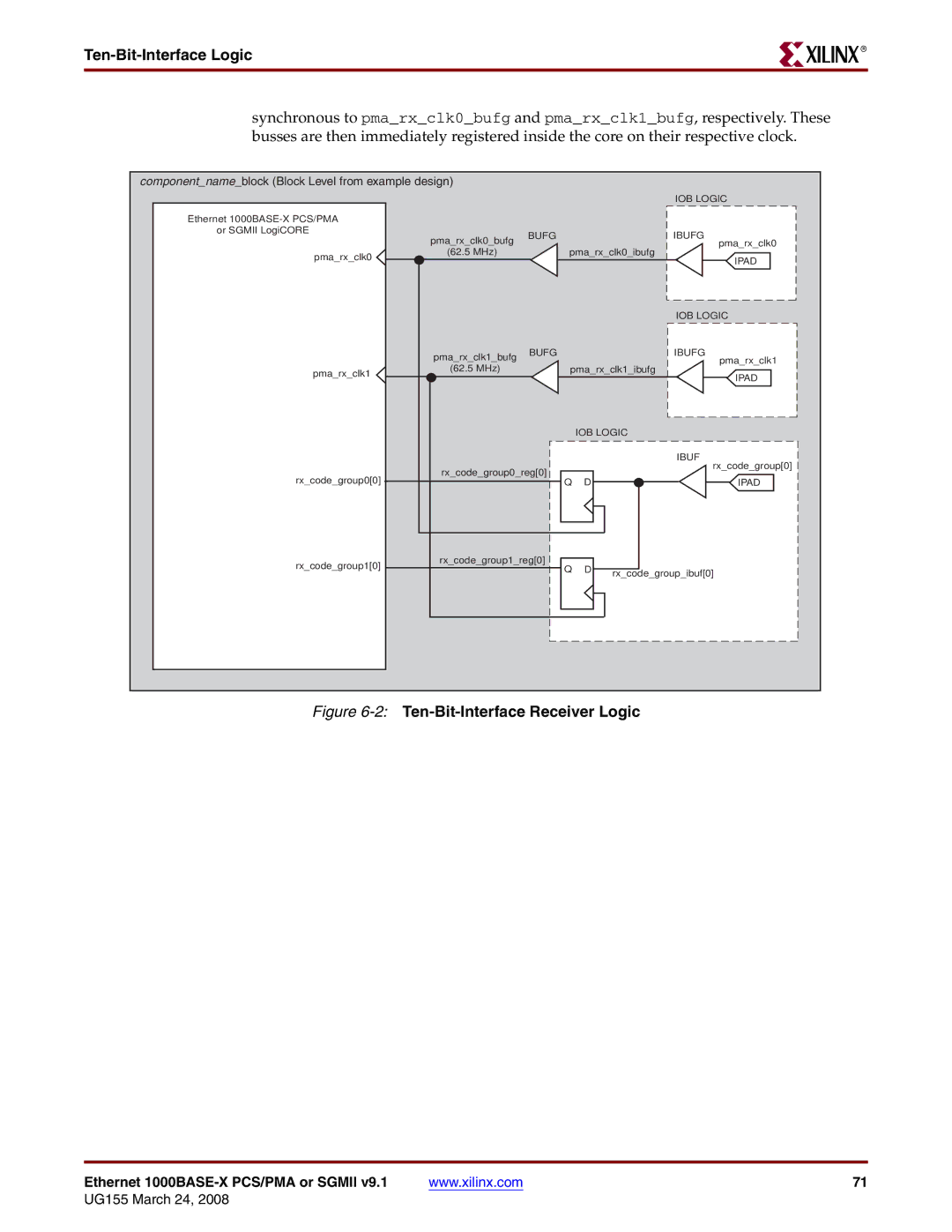

Ten-Bit-Interface Logic

R

synchronous to pma_rx_clk0_bufg and pma_rx_clk1_bufg, respectively. These busses are then immediately registered inside the core on their respective clock.

component_name_block (Block Level from example design)

IOB LOGIC

Ethernet |

|

|

|

|

|

|

or SGMII LogiCORE | pma_rx_clk0_bufg | BUFG |

|

|

| IBUFG |

|

|

|

| |||

|

| pma_rx_clk0_ibufg | pma_rx_clk0 | |||

pma_rx_clk0 | (62.5 MHz) |

| IPAD | |||

|

|

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

|

| IOB LOGIC |

| pma_rx_clk1_bufg | BUFG |

|

|

| IBUFG |

|

|

|

|

| pma_rx_clk1 | |

| (62.5 MHz) |

| pma_rx_clk1_ibufg | |||

pma_rx_clk1 |

| IPAD | ||||

|

|

|

|

| ||

|

|

|

|

|

| |

|

|

|

| IOB LOGIC |

| |

|

|

|

|

|

| IBUF |

| rx_code_group0_reg[0] |

|

|

| rx_code_group[0] | |

rx_code_group0[0] | Q | D |

| IPAD | ||

|

|

| ||||

rx_code_group1[0] | rx_code_group1_reg[0] | Q | D |

|

| |

|

| rx_code_group_ibuf[0] | ||||

|

|

| ||||

|

|

|

|

| ||

Figure 6-2: Ten-Bit-Interface Receiver Logic

Ethernet | www.xilinx.com | 71 |