Core Interfaces

R

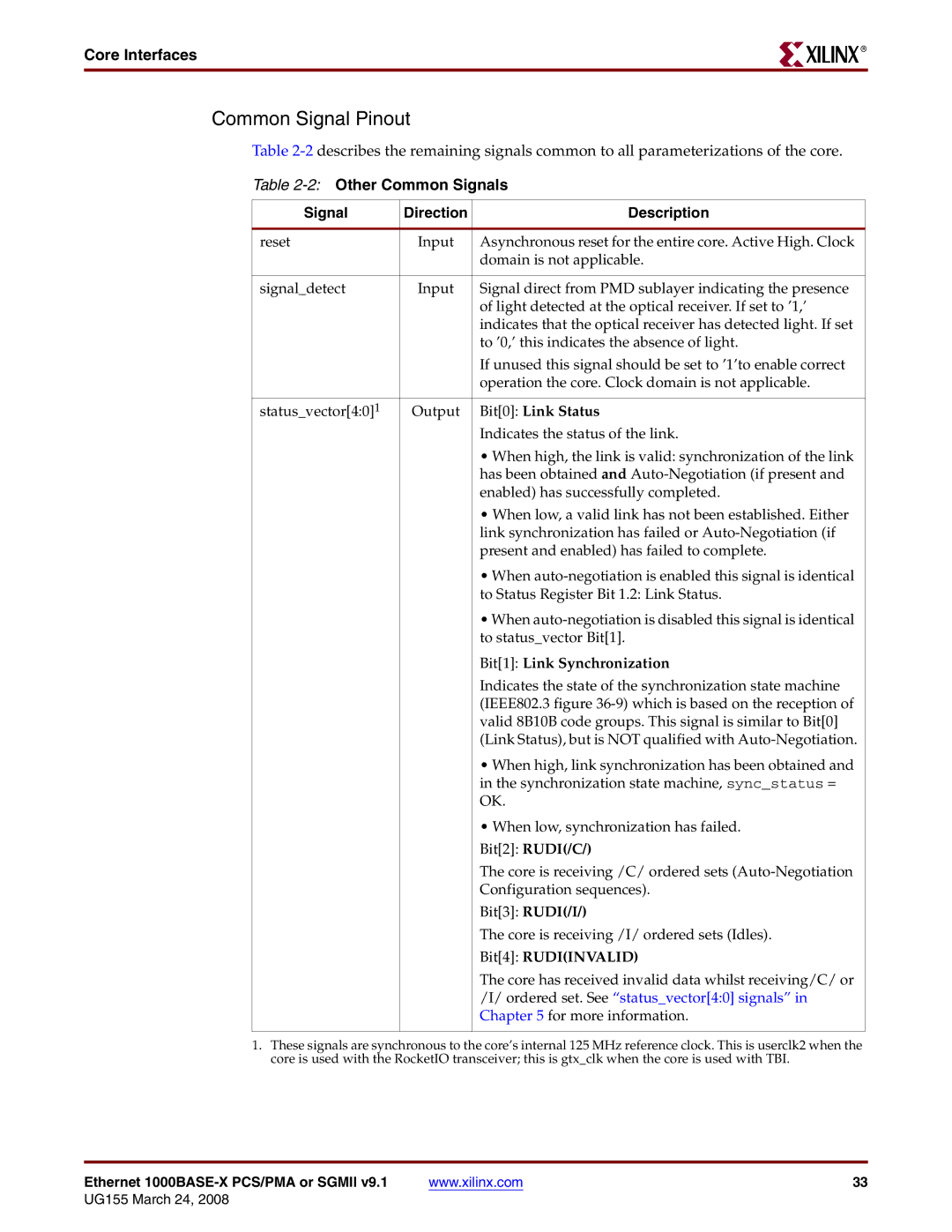

Common Signal Pinout

Table

Table 2-2: Other Common Signals

Signal | Direction | Description |

|

|

|

reset | Input | Asynchronous reset for the entire core. Active High. Clock |

|

| domain is not applicable. |

|

|

|

signal_detect | Input | Signal direct from PMD sublayer indicating the presence |

|

| of light detected at the optical receiver. If set to ’1,’ |

|

| indicates that the optical receiver has detected light. If set |

|

| to ’0,’ this indicates the absence of light. |

|

| If unused this signal should be set to ’1’to enable correct |

|

| operation the core. Clock domain is not applicable. |

|

|

|

status_vector[4:0]1 | Output | Bit[0]: Link Status |

|

| Indicates the status of the link. |

|

| • When high, the link is valid: synchronization of the link |

|

| has been obtained and |

|

| enabled) has successfully completed. |

|

| • When low, a valid link has not been established. Either |

|

| link synchronization has failed or |

|

| present and enabled) has failed to complete. |

|

| • When |

|

| to Status Register Bit 1.2: Link Status. |

|

| • When |

|

| to status_vector Bit[1]. |

|

| Bit[1]: Link Synchronization |

|

| Indicates the state of the synchronization state machine |

|

| (IEEE802.3 figure |

|

| valid 8B10B code groups. This signal is similar to Bit[0] |

|

| (Link Status), but is NOT qualified with |

|

| • When high, link synchronization has been obtained and |

|

| in the synchronization state machine, sync_status = |

|

| OK. |

|

| • When low, synchronization has failed. |

|

| Bit[2]: RUDI(/C/) |

|

| The core is receiving /C/ ordered sets |

|

| Configuration sequences). |

|

| Bit[3]: RUDI(/I/) |

|

| The core is receiving /I/ ordered sets (Idles). |

|

| Bit[4]: RUDI(INVALID) |

|

| The core has received invalid data whilst receiving/C/ or |

|

| /I/ ordered set. See “status_vector[4:0] signals” in |

|

| Chapter 5 for more information. |

|

|

|

1.These signals are synchronous to the core’s internal 125 MHz reference clock. This is userclk2 when the core is used with the RocketIO transceiver; this is gtx_clk when the core is used with TBI.

Ethernet | www.xilinx.com | 33 |