R

Chapter 8: SGMII / Dynamic Standards Switching with RocketIO Transceivers

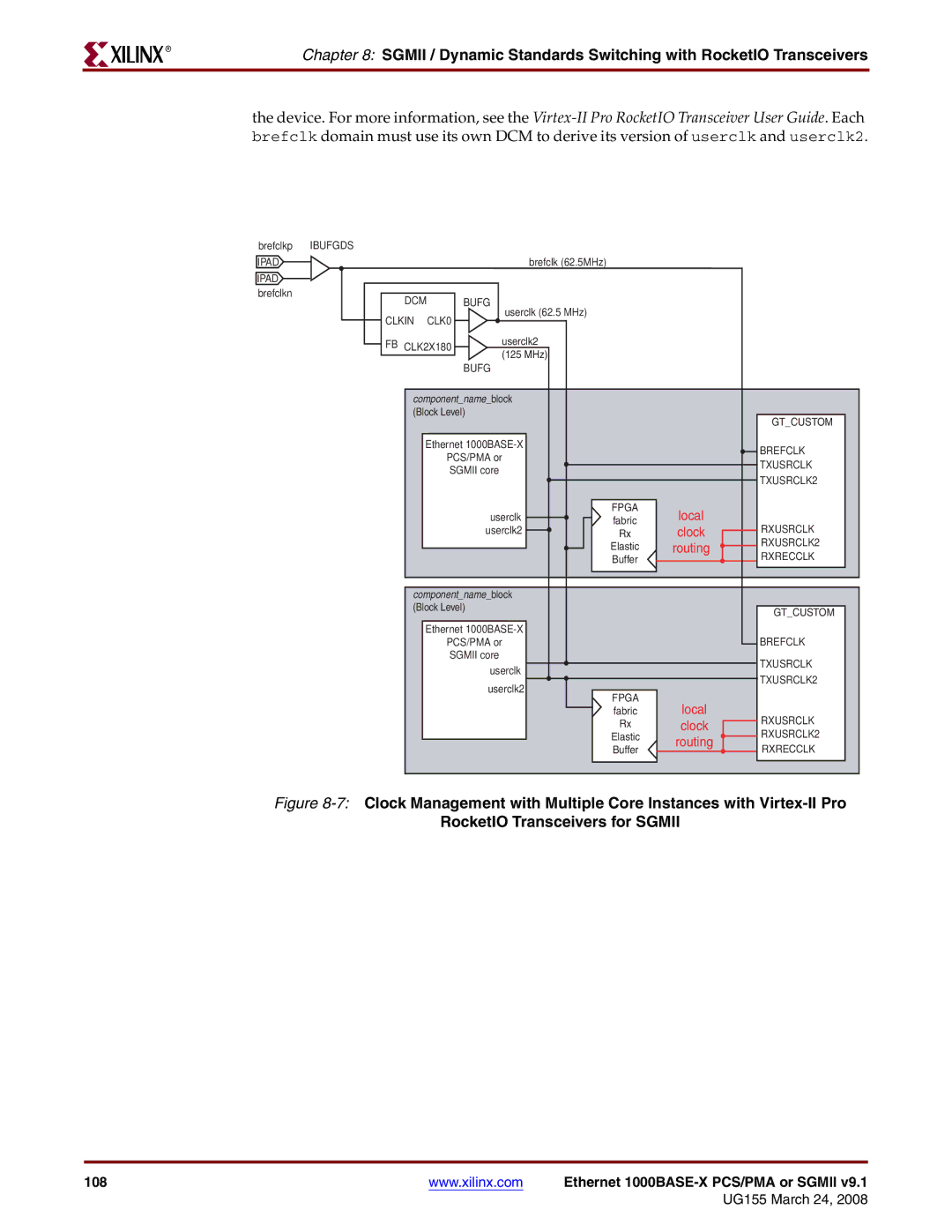

the device. For more information, see the

brefclkp IBUFGDS IPAD

IPAD brefclkn

brefclk (62.5MHz)

DCM |

| BUFG |

|

|

|

CLKIN | CLK0 | userclk (62.5 MHz) |

|

|

|

|

|

|

| ||

FB CLK2X180 | userclk2 |

|

|

| |

(125 MHz) |

|

|

| ||

|

|

|

|

| |

|

| BUFG |

|

|

|

component_name_block |

|

|

| ||

(Block Level) |

|

| GT_CUSTOM | ||

|

|

|

|

| |

Ethernet |

|

| BREFCLK | ||

| PCS/PMA or |

|

| ||

|

|

| TXUSRCLK | ||

| SGMII core |

|

| ||

|

|

| TXUSRCLK2 | ||

|

|

|

|

| |

|

| userclk | FPGA | local |

|

|

| fabric | RXUSRCLK | ||

|

| userclk2 | Rx | clock | |

|

|

| Elastic | routing | RXUSRCLK2 |

|

|

| RXRECCLK | ||

|

|

| Buffer |

| |

component_name_block |

|

|

| ||

(Block Level) |

|

| GT_CUSTOM | ||

|

|

|

|

| |

Ethernet |

|

| BREFCLK | ||

| PCS/PMA or |

|

| ||

| SGMII core |

|

| TXUSRCLK | |

|

| userclk |

|

| |

|

|

|

| TXUSRCLK2 | |

|

| userclk2 |

|

| |

|

| FPGA |

|

| |

|

|

| local |

| |

|

|

| fabric | RXUSRCLK | |

|

|

| Rx | clock | |

|

|

| RXUSRCLK2 | ||

|

|

| Elastic | routing | |

|

|

| Buffer | RXRECCLK | |

|

|

|

| ||

Figure 8-7: Clock Management with Multiple Core Instances with Virtex-II Pro

RocketIO Transceivers for SGMII

108 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |