Integrating with the 1-Gigabit Ethernet MAC Core

R

Integration of the

Virtex-II Pro Devices

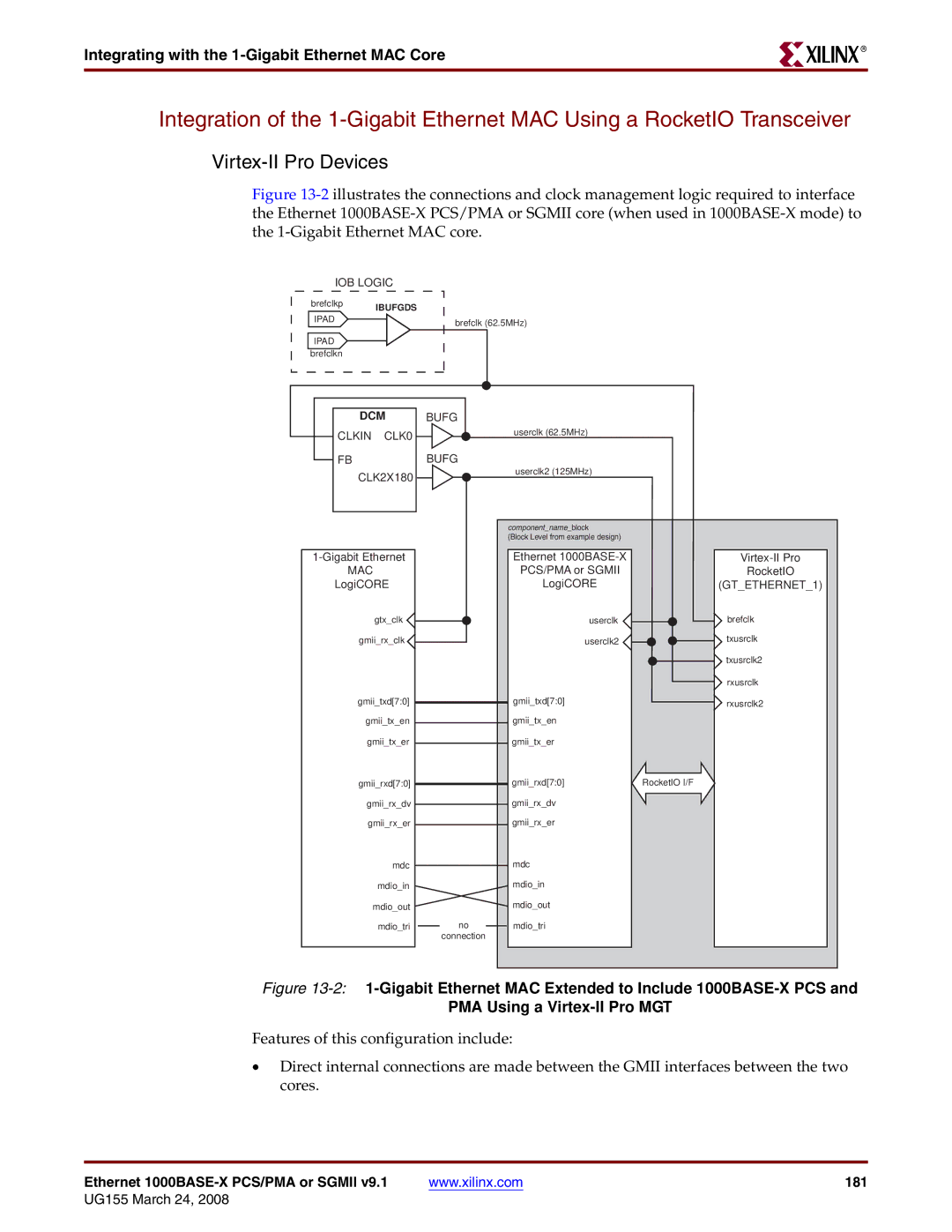

Figure 13-2 illustrates the connections and clock management logic required to interface the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in 1000BASE-X mode) to the 1-Gigabit Ethernet MAC core.

IOB LOGIC

brefclkp IBUFGDS

IPAD | brefclk (62.5MHz) |

|

IPAD brefclkn

DCM

CLKIN CLK0

FB

CLK2X180

BUFG

BUFG

userclk (62.5MHz)

userclk2 (125MHz)

component_name_block

(Block Level from example design)

MAC

LogiCORE

gtx_clk gmii_rx_clk ![]()

gmii_txd[7:0] gmii_tx_en gmii_tx_er

gmii_rxd[7:0] gmii_rx_dv gmii_rx_er

mdc mdio_in mdio_out mdio_tri

no

connection

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

userclk

userclk2

gmii_txd[7:0] gmii_tx_en gmii_tx_er

gmii_rxd[7:0] gmii_rx_dv gmii_rx_er

mdc mdio_in mdio_out mdio_tri

RocketIO I/F

RocketIO

(GT_ETHERNET_1)

brefclk

txusrclk

txusrclk2

rxusrclk

rxusrclk2

Figure 13-2: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and

PMA Using a Virtex-II Pro MGT

Features of this configuration include:

•Direct internal connections are made between the GMII interfaces between the two cores.

Ethernet | www.xilinx.com | 181 |