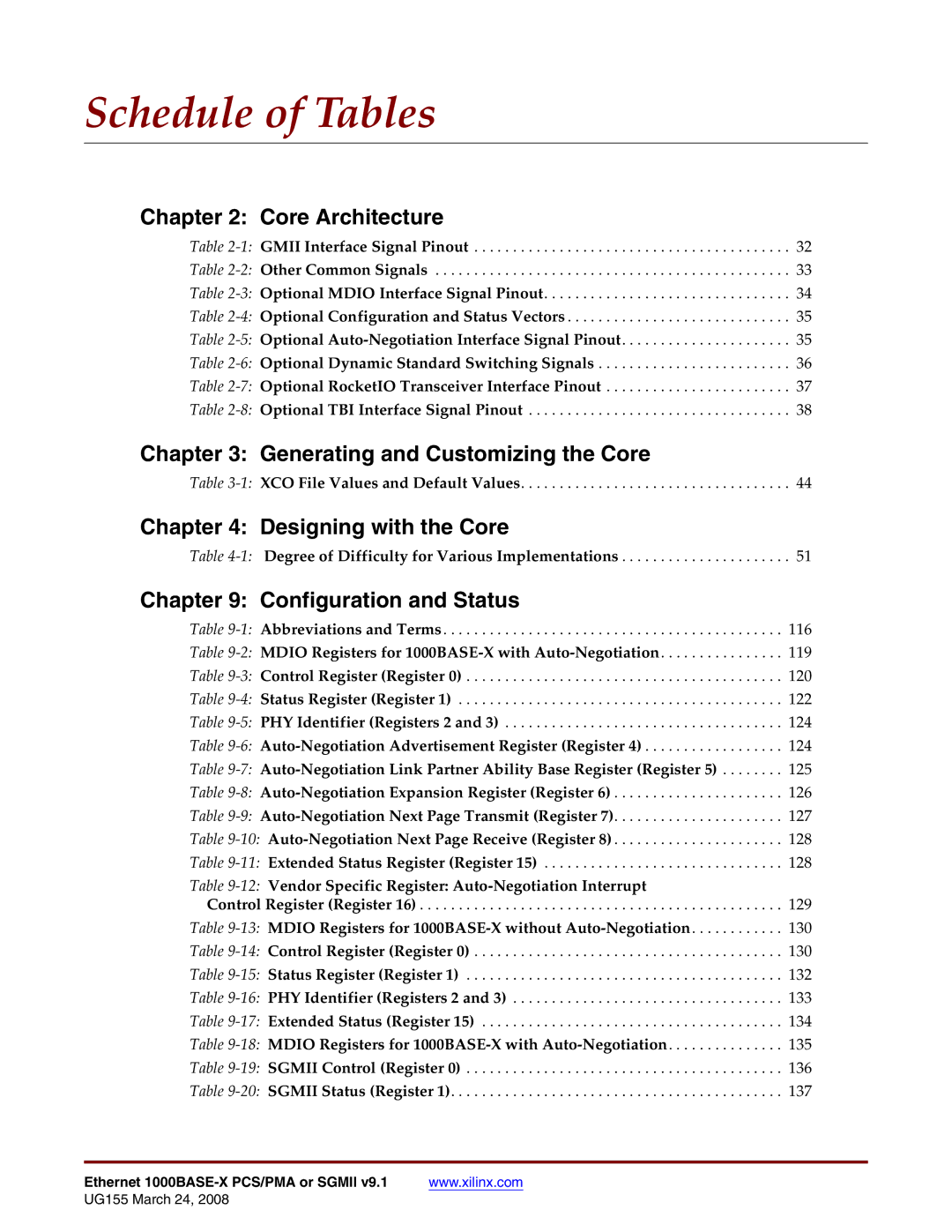

Schedule of Tables

Chapter 2: Core Architecture

Table

Table

Table

Table

Table 2-5: Optional Auto-Negotiation Interface Signal Pinout. . . . . . . . . . . . . . . . . . . . . . 35

Table

Table

Table

Chapter 3: Generating and Customizing the Core

Table

Chapter 4: Designing with the Core |

|

Table | . 51 |

Chapter 9: Configuration and Status |

|

Table | 116 |

Table | 119 |

Table | 120 |

Table | 122 |

Table | 124 |

Table | 124 |

Table | 125 |

Table | 126 |

Table | 127 |

Table | 128 |

Table | 128 |

Table |

|

Control Register (Register 16) | 129 |

Table | 130 |

Table | 130 |

Table | 132 |

Table | 133 |

Table | 134 |

Table | 135 |

Table | 136 |

Table | 137 |

Ethernet | www.xilinx.com |