Required Constraints

R

GMII_TX_CLK

Data Sheet report:

All values displayed in nanoseconds (ns)

Setup/Hold to | clock gmii_tx_clk |

|

|

| ||

+ | + | + | ||||

| Setup to | Hold to | Clock | |||

Source | clk (edge) clk (edge) Internal Clock(s) | Phase | ||||

+ | + | + | ||||

gmii_tx_en | 7.875(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_tx_er | 7.878(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<0> | 7.880(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<1> | 7.893(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<2> | 7.890(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<3> | 7.889(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<4> | 7.894(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<5> | 7.895(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<6> | 7.889(R)gmii_tx_clk_bufg | 0.000 | ||||

gmii_txd<7> | 7.889(R)gmii_tx_clk_bufg | 0.000 | ||||

+ | + | + | ||||

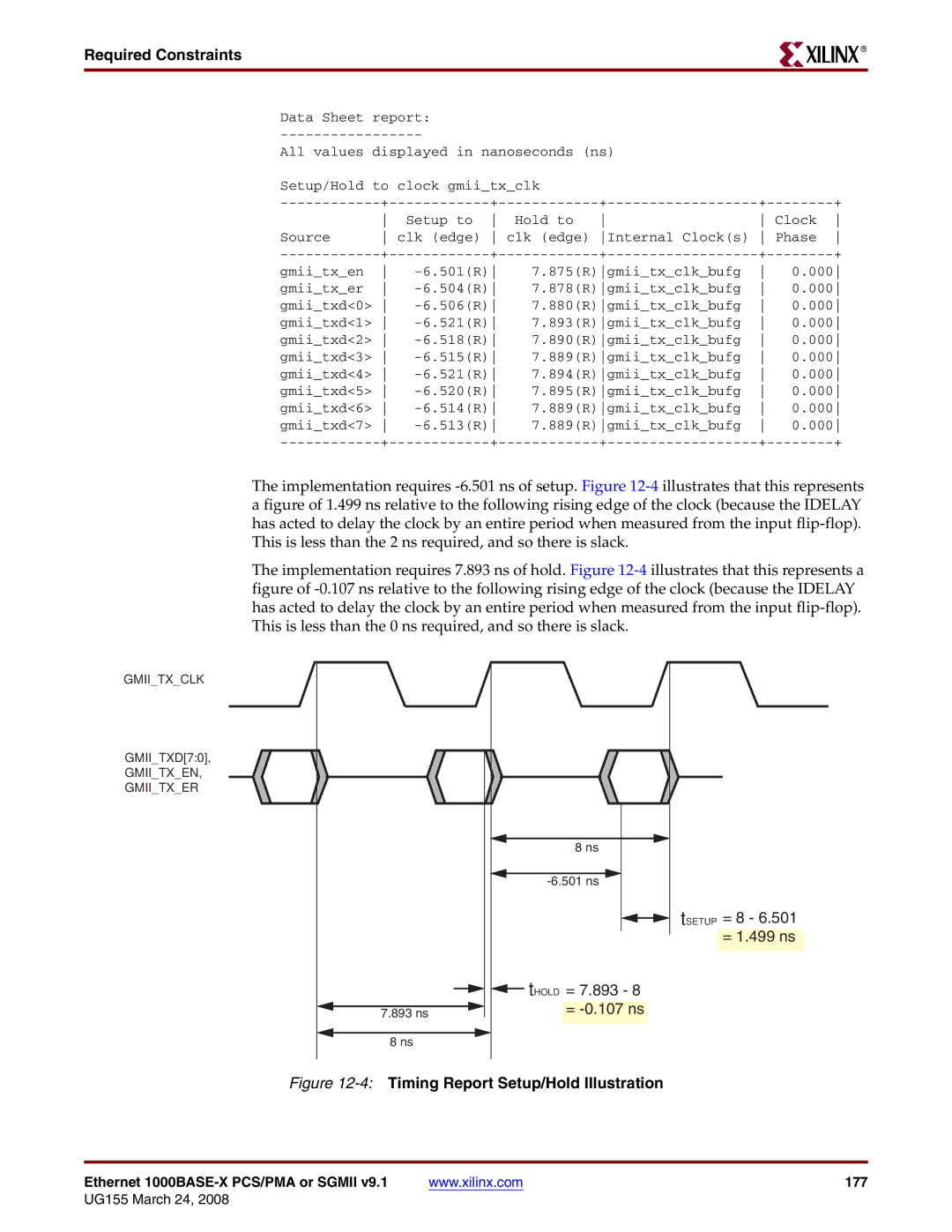

The implementation requires

The implementation requires 7.893 ns of hold. Figure

GMII_TXD[7:0], GMII_TX_EN, GMII_TX_ER

8 ns |

|

|

|

|

| tHOLD = 7.893 - 8 | |

|

|

|

|

| ||

|

|

|

|

|

| = |

7.893 ns | ||||||

|

|

|

|

|

|

|

tSETUP = 8 - 6.501 = 1.499 ns

8 ns

Figure 12-4: Timing Report Setup/Hold Illustration

Ethernet | www.xilinx.com | 177 |