R

Chapter 2: Core Architecture

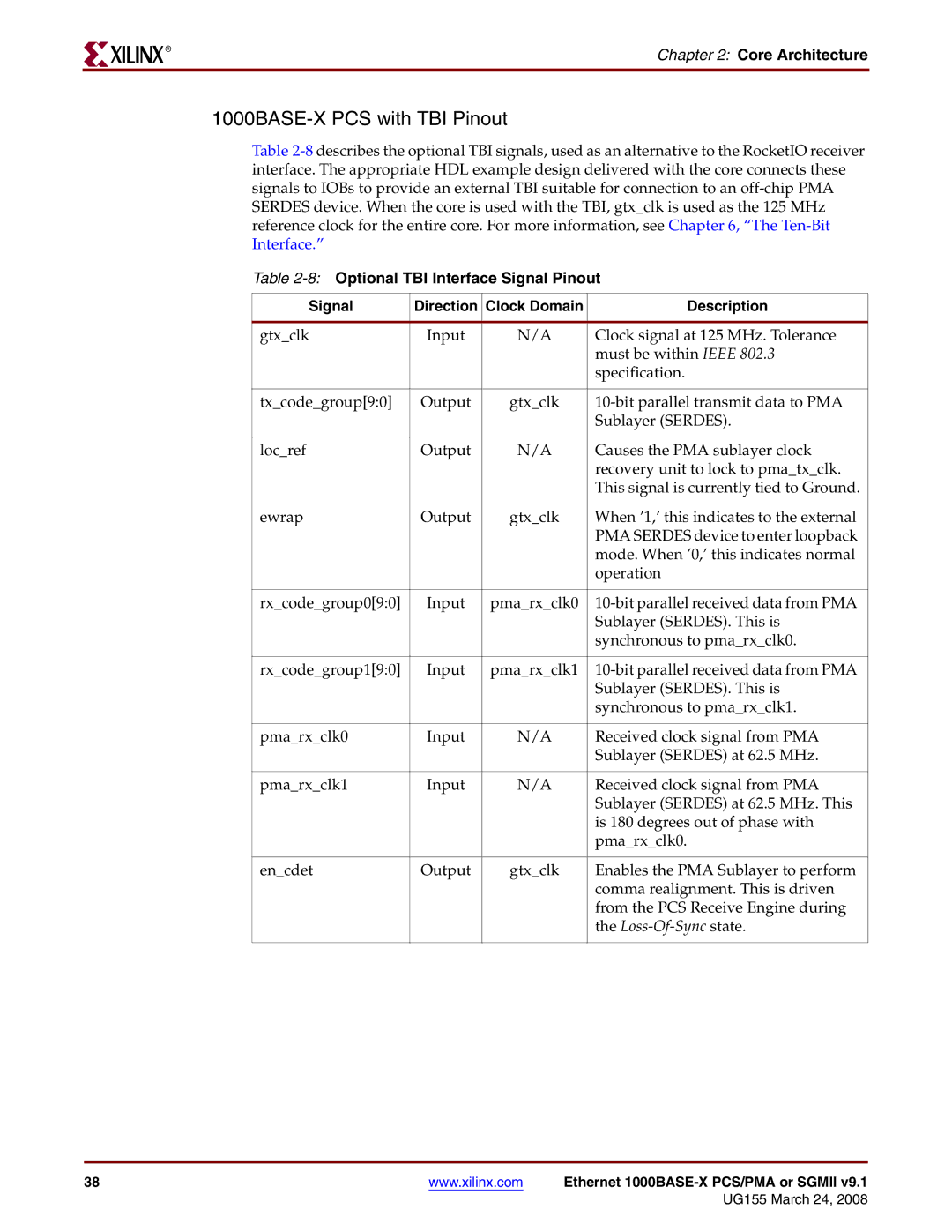

1000BASE-X PCS with TBI Pinout

Table

Table

Signal | Direction | Clock Domain | Description |

|

|

|

|

gtx_clk | Input | N/A | Clock signal at 125 MHz. Tolerance |

|

|

| must be within IEEE 802.3 |

|

|

| specification. |

|

|

|

|

tx_code_group[9:0] | Output | gtx_clk | |

|

|

| Sublayer (SERDES). |

|

|

|

|

loc_ref | Output | N/A | Causes the PMA sublayer clock |

|

|

| recovery unit to lock to pma_tx_clk. |

|

|

| This signal is currently tied to Ground. |

|

|

|

|

ewrap | Output | gtx_clk | When ’1,’ this indicates to the external |

|

|

| PMA SERDES device to enter loopback |

|

|

| mode. When ’0,’ this indicates normal |

|

|

| operation |

|

|

|

|

rx_code_group0[9:0] | Input | pma_rx_clk0 | |

|

|

| Sublayer (SERDES). This is |

|

|

| synchronous to pma_rx_clk0. |

|

|

|

|

rx_code_group1[9:0] | Input | pma_rx_clk1 | |

|

|

| Sublayer (SERDES). This is |

|

|

| synchronous to pma_rx_clk1. |

|

|

|

|

pma_rx_clk0 | Input | N/A | Received clock signal from PMA |

|

|

| Sublayer (SERDES) at 62.5 MHz. |

|

|

|

|

pma_rx_clk1 | Input | N/A | Received clock signal from PMA |

|

|

| Sublayer (SERDES) at 62.5 MHz. This |

|

|

| is 180 degrees out of phase with |

|

|

| pma_rx_clk0. |

|

|

|

|

en_cdet | Output | gtx_clk | Enables the PMA Sublayer to perform |

|

|

| comma realignment. This is driven |

|

|

| from the PCS Receive Engine during |

|

|

| the |

|

|

|

|

38 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |