Management Registers

R

SGMII Standard Using the Optional Auto-Negotiation

The registers provided for SGMII operation in this core are adaptations of those defined in IEEE 802.3 clauses 37 and 22. In an SGMII implementation, two different types of links exist. They are the SGMII link between the MAC and PHY (SGMII link) and the link across the Ethernet Medium itself (Medium). See Figure

Information regarding the state of both of these links is contained within the following registers. Where applicable, the abbreviations SGMII link and Medium are used in the register descriptions. Registers at undefined addresses are

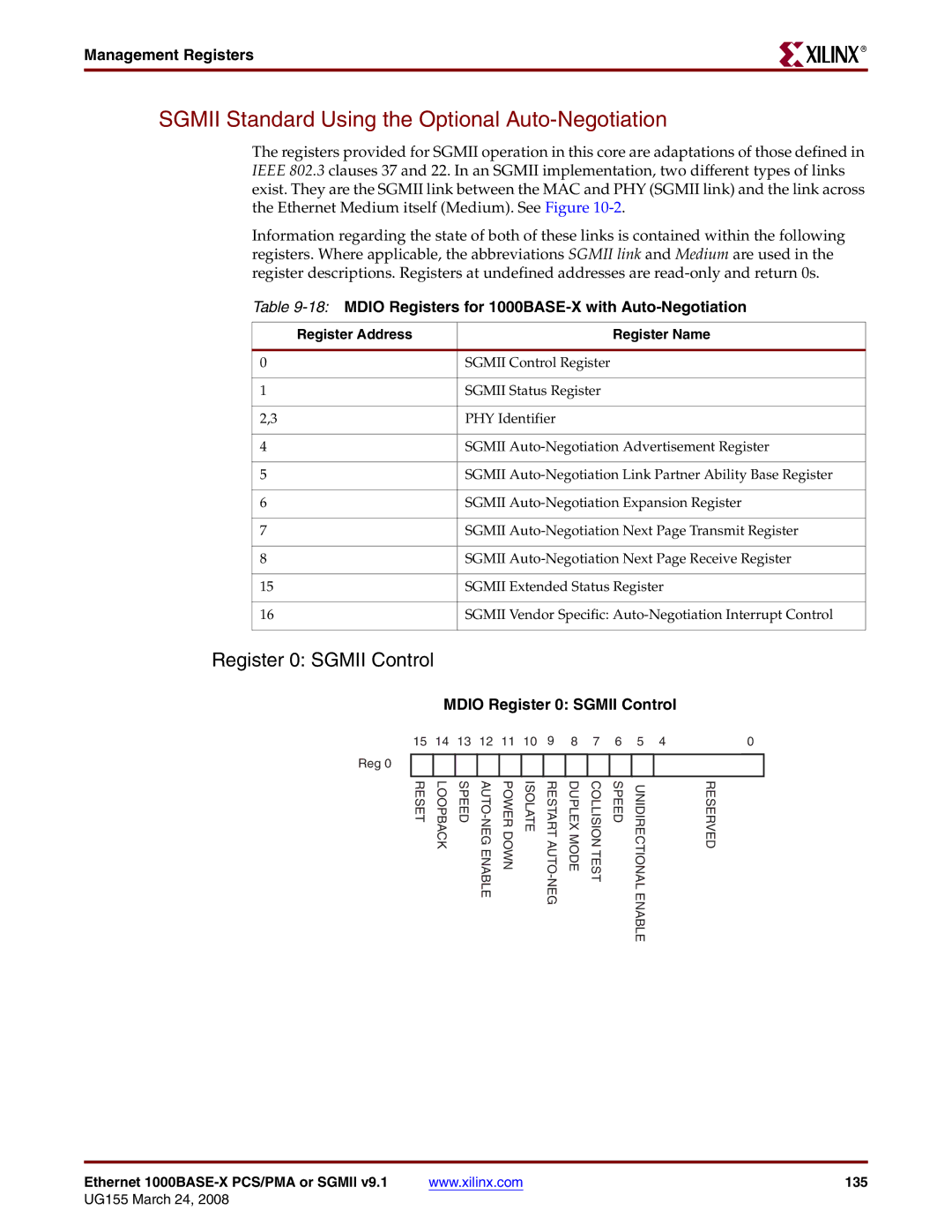

Table 9-18: MDIO Registers for 1000BASE-X with Auto-Negotiation

Register Address | Register Name |

|

|

0 | SGMII Control Register |

|

|

1 | SGMII Status Register |

|

|

2,3 | PHY Identifier |

|

|

4 | SGMII |

|

|

5 | SGMII |

|

|

6 | SGMII |

|

|

7 | SGMII |

|

|

8 | SGMII |

|

|

15 | SGMII Extended Status Register |

|

|

16 | SGMII Vendor Specific: |

|

|

Register 0: SGMII Control

MDIO Register 0: SGMII Control

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Reg 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RESET | LOOPBACK | SPEED | POWER DOWN | ISOLATE | RESTART | DUPLEX MODE | COLLISION TEST | SPEED | UNIDIRECTIONAL ENABLE |

| RESERVED | |

Ethernet | www.xilinx.com | 135 |