R

Chapter 9: Configuration and Status

Table 9-2: MDIO Registers for 1000BASE-X with Auto-Negotiation (Continued)

Register Address | Register Name |

|

|

2,3 | PHY Identifier |

|

|

4 | |

|

|

5 | |

|

|

6 | |

|

|

7 | |

|

|

8 | |

|

|

15 | Extended Status Register |

|

|

16 | Vendor Specific: |

|

|

Register 0: Control Register

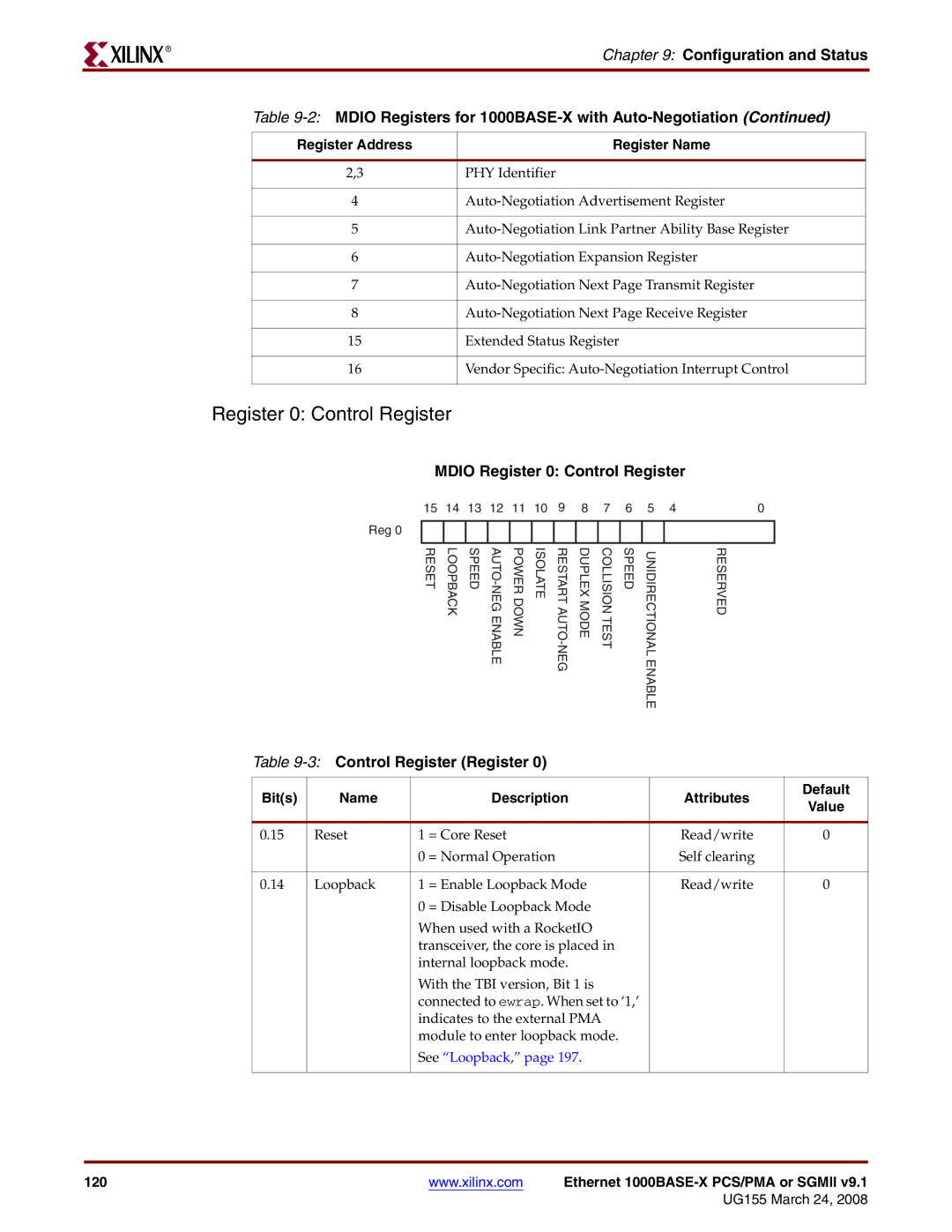

MDIO Register 0: Control Register

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Reg 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RESET | LOOPBACK | SPEED | POWER DOWN | ISOLATE | RESTART | DUPLEX MODE | COLLISION TEST | SPEED | UNIDIRECTIONAL ENABLE |

| RESERVED | |

Table 9-3: Control Register (Register 0)

Bit(s) | Name |

| Description | Attributes | Default |

| Value | ||||

|

|

|

|

| |

|

|

|

|

|

|

0.15 | Reset | 1 | = Core Reset | Read/write | 0 |

|

| 0 | = Normal Operation | Self clearing |

|

|

|

|

|

|

|

0.14 | Loopback | 1 | = Enable Loopback Mode | Read/write | 0 |

|

| 0 | = Disable Loopback Mode |

|

|

|

| When used with a RocketIO |

|

| |

|

| transceiver, the core is placed in |

|

| |

|

| internal loopback mode. |

|

| |

|

| With the TBI version, Bit 1 is |

|

| |

|

| connected to ewrap. When set to ‘1,’ |

|

| |

|

| indicates to the external PMA |

|

| |

|

| module to enter loopback mode. |

|

| |

|

| See “Loopback,” page 197. |

|

| |

|

|

|

|

|

|

120 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |