Designing with the

R

Bits[4:2]: Code Group Reception Indicators

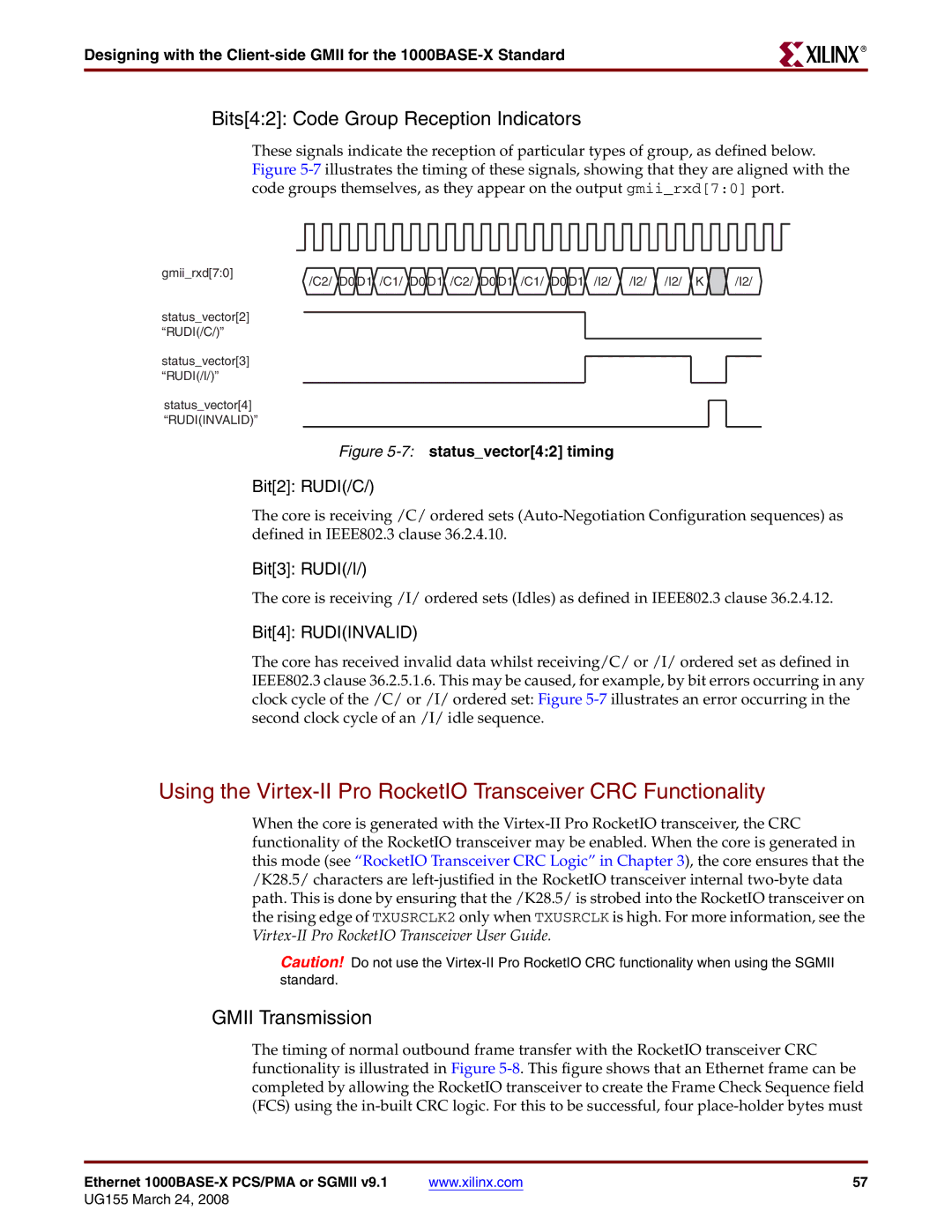

These signals indicate the reception of particular types of group, as defined below. Figure

gmii_rxd[7:0] | /C2/ D0 D1 /C1/ D0 D1 /I2/ /I2/ /I2/ K | /I2/ |

/C2/ D0 D1 /C1/ D0 D1 |

status_vector[2] “RUDI(/C/)”

status_vector[3] “RUDI(/I/)”

status_vector[4] “RUDI(INVALID)”

Figure 5-7: status_vector[4:2] timing

Bit[2]: RUDI(/C/)

The core is receiving /C/ ordered sets

Bit[3]: RUDI(/I/)

The core is receiving /I/ ordered sets (Idles) as defined in IEEE802.3 clause 36.2.4.12.

Bit[4]: RUDI(INVALID)

The core has received invalid data whilst receiving/C/ or /I/ ordered set as defined in IEEE802.3 clause 36.2.5.1.6. This may be caused, for example, by bit errors occurring in any clock cycle of the /C/ or /I/ ordered set: Figure

Using the

When the core is generated with the

Caution! Do not use the

GMII Transmission

The timing of normal outbound frame transfer with the RocketIO transceiver CRC functionality is illustrated in Figure

Ethernet | www.xilinx.com | 57 |