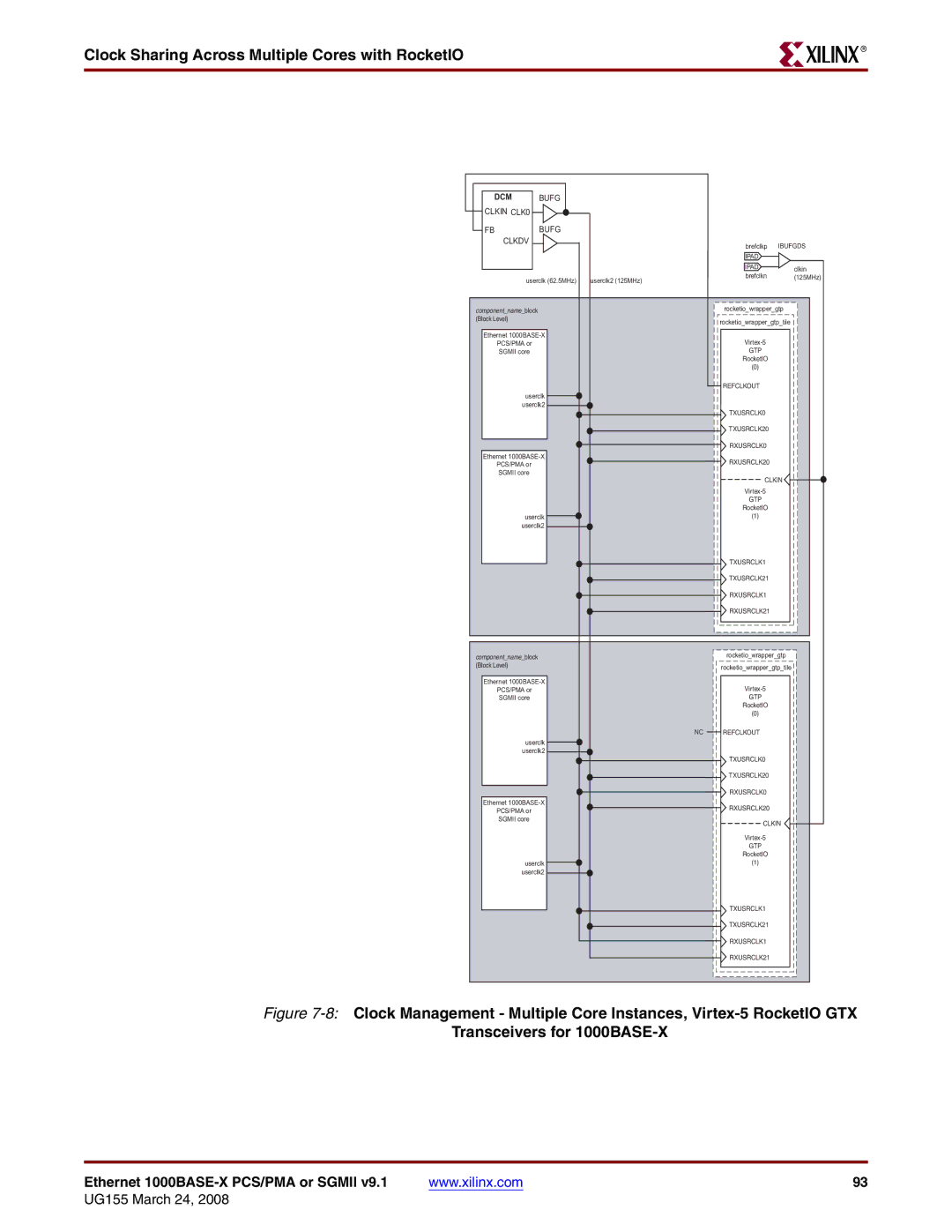

Clock Sharing Across Multiple Cores with RocketIO

R

DCM | BUFG |

CLKIN CLK0

FB | BUFG |

|

|

|

| CLKDV |

| brefclkp | IBUFGDS |

|

|

| ||

|

|

| IPAD |

|

|

|

| IPAD | clkin |

| userclk (62.5MHz) | userclk2 (125MHz) | brefclkn | (125MHz) |

|

|

| ||

component_name_block |

| rocketio_wrapper_gtp | ||

(Block Level) |

| rocketio_wrapper_gtp_tile | ||

|

|

| ||

Ethernet |

|

| ||

| PCS/PMA or |

|

| |

| SGMII core |

| GTP |

|

|

|

| RocketIO |

|

|

|

| (0) |

|

|

|

| REFCLKOUT |

|

| userclk |

|

|

|

| userclk2 |

|

|

|

|

|

| TXUSRCLK0 |

|

|

|

| TXUSRCLK20 |

|

|

|

| RXUSRCLK0 |

|

Ethernet |

| RXUSRCLK20 |

| |

| PCS/PMA or |

|

| |

|

|

|

| |

| SGMII core |

| CLKIN | |

|

|

| ||

|

|

|

| |

|

|

| GTP |

|

|

|

| RocketIO |

|

| userclk |

| (1) |

|

| userclk2 |

|

|

|

|

|

| TXUSRCLK1 |

|

|

|

| TXUSRCLK21 |

|

|

|

| RXUSRCLK1 |

|

|

|

| RXUSRCLK21 |

|

component_name_block |

| rocketio_wrapper_gtp | ||

(Block Level) |

| rocketio_wrapper_gtp_tile | ||

Ethernet |

|

| ||

| PCS/PMA or |

|

| |

| SGMII core |

| GTP |

|

|

|

| RocketIO |

|

|

|

| (0) |

|

|

| NC | REFCLKOUT |

|

| userclk |

|

|

|

| userclk2 |

|

|

|

|

|

| TXUSRCLK0 |

|

|

|

| TXUSRCLK20 |

|

|

|

| RXUSRCLK0 |

|

Ethernet |

| RXUSRCLK20 |

| |

| PCS/PMA or |

|

| |

|

|

|

| |

| SGMII core |

| CLKIN | |

|

|

| ||

|

|

|

| |

|

|

| GTP |

|

|

|

| RocketIO |

|

| userclk |

| (1) |

|

| userclk2 |

|

|

|

|

|

| TXUSRCLK1 |

|

|

|

| TXUSRCLK21 |

|

|

|

| RXUSRCLK1 |

|

|

|

| RXUSRCLK21 |

|

Figure 7-8: Clock Management - Multiple Core Instances, Virtex-5 RocketIO GTX

Transceivers for 1000BASE-X

Ethernet | www.xilinx.com | 93 |