R

Chapter 13: Interfacing to Other Cores

•If both cores have been generated with the optional management interface, the MDIO port can be connected up to that of the

•Due to the embedded Receiver Elastic Buffer in the MGT, the entire GMII is synchronous to a

Virtex-4 Devices

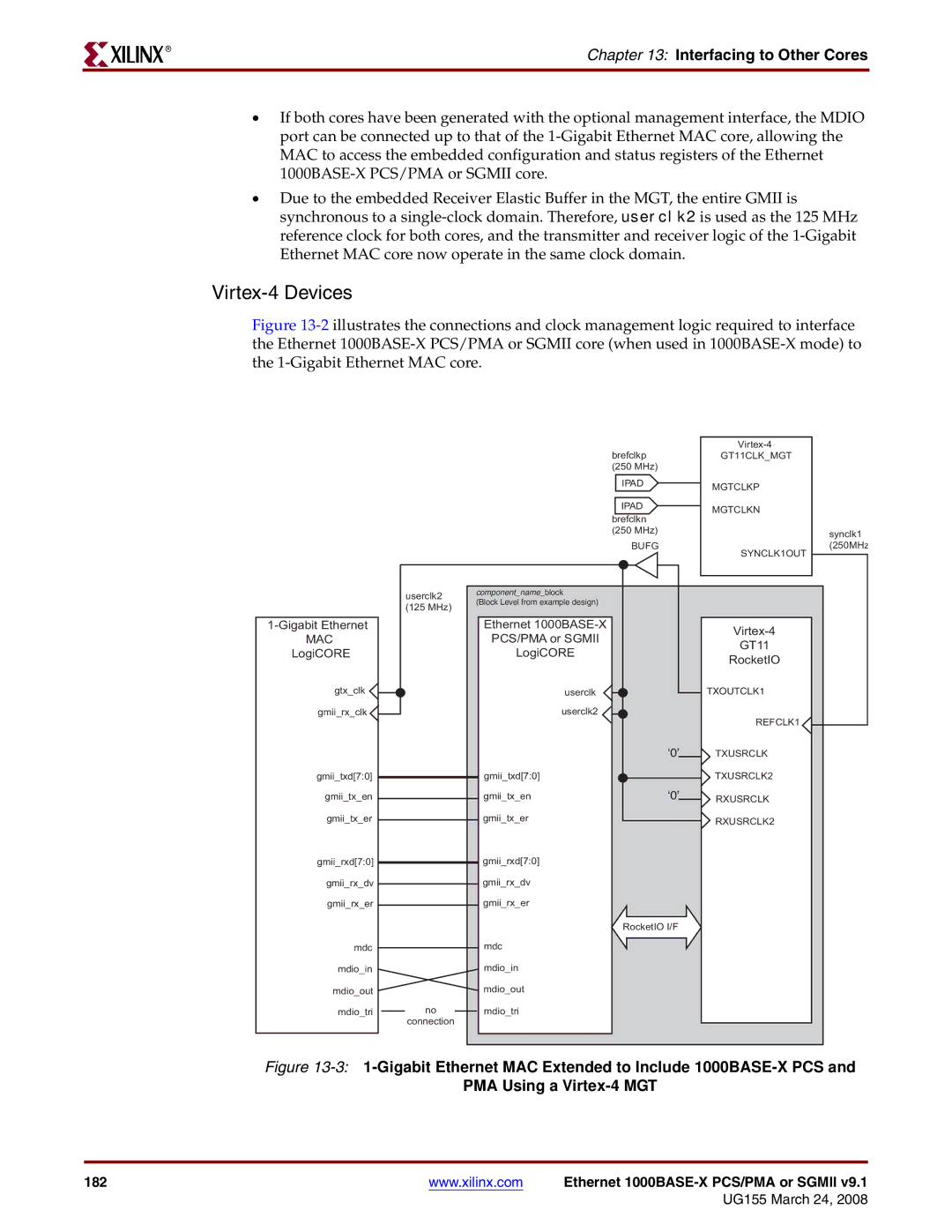

Figure 13-2 illustrates the connections and clock management logic required to interface the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in 1000BASE-X mode) to the 1-Gigabit Ethernet MAC core.

MAC

LogiCORE

gtx_clk

gmii_rx_clk

gmii_txd[7:0] gmii_tx_en

gmii_tx_er

gmii_rxd[7:0]

gmii_rx_dv gmii_rx_er

mdc

mdio_in

mdio_out mdio_tri

|

| brefclkp |

|

| (250 MHz) |

|

| IPAD |

|

| IPAD |

|

| brefclkn |

|

| (250 MHz) |

|

| BUFG |

userclk2 | component_name_block |

|

(Block Level from example design) |

| |

(125 MHz) |

| |

|

| |

| Ethernet |

|

| PCS/PMA or SGMII |

|

| LogiCORE |

|

| userclk |

|

| userclk2 |

|

|

| ‘0’ |

| gmii_txd[7:0] |

|

| gmii_tx_en | ‘0’ |

| gmii_tx_er |

|

| gmii_rxd[7:0] |

|

| gmii_rx_dv |

|

| gmii_rx_er |

|

|

| RocketIO I/F |

| mdc |

|

| mdio_in |

|

| mdio_out |

|

no | mdio_tri |

|

connection |

|

|

GT11CLK_MGT

MGTCLKP

MGTCLKN

SYNCLK1OUT

GT11

RocketIO

TXOUTCLK1

REFCLK1 ![]()

TXUSRCLK

TXUSRCLK2

RXUSRCLK

RXUSRCLK2

synclk1

(250MHz

Figure 13-3: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and

PMA Using a Virtex-4 MGT

182 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |