R

Chapter 12: Constraining the Core

INST "gmii_data_bus[6].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[5].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[4].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[3].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[2].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[1].delay_gmii_txd" IDELAY_VALUE = "33";

INST "gmii_data_bus[0].delay_gmii_txd" IDELAY_VALUE = "33";

The value of IDELAY_VALUE for the gmii_tx_clk clock is preconfigured in the example designs to meet the setup and hold constraints for the example GMII pinout in the particular device. The setup/hold timing which is achieved after

Understanding Timing Reports for Setup/Hold Timing

Devices Other Than Virtex-4 or Virtex-5

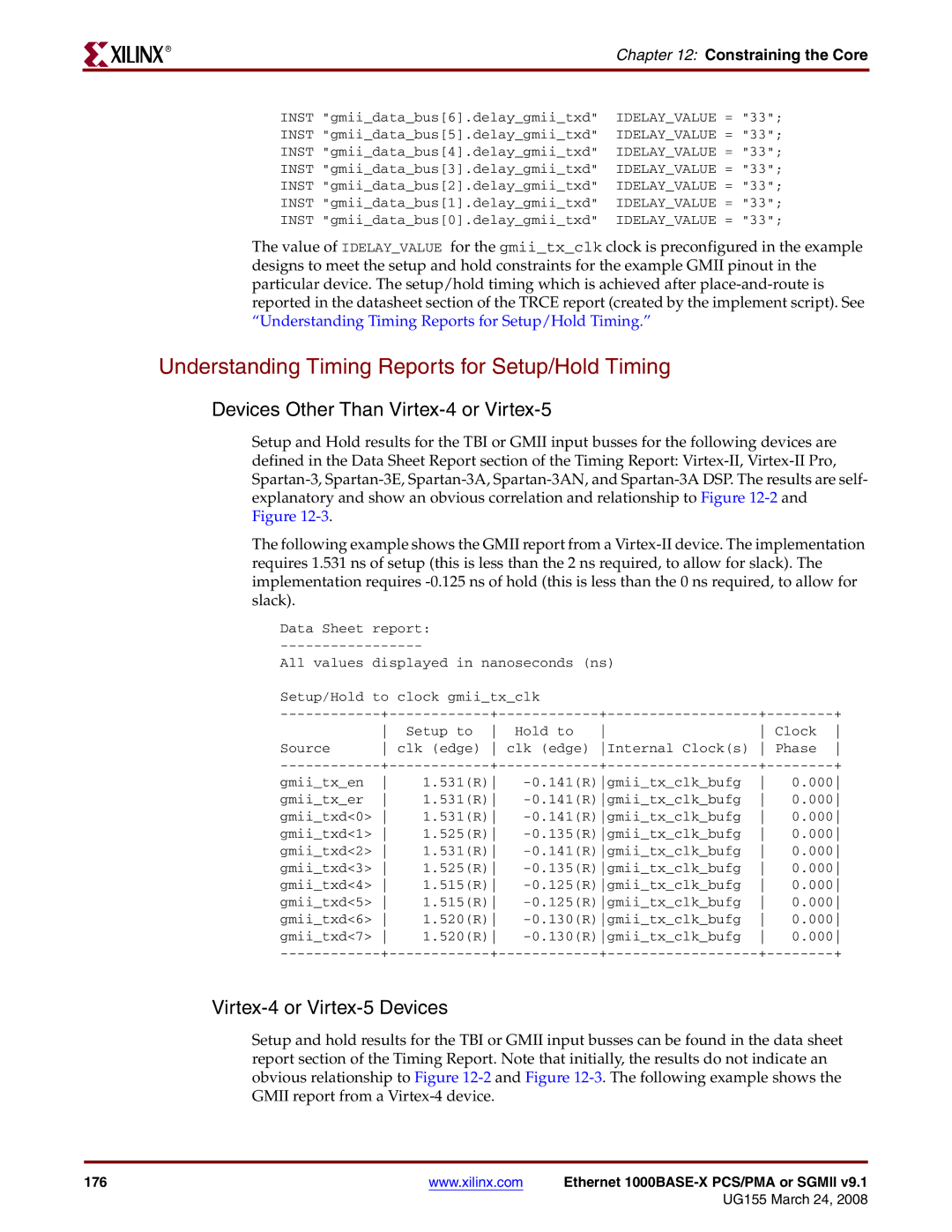

Setup and Hold results for the TBI or GMII input busses for the following devices are defined in the Data Sheet Report section of the Timing Report:

The following example shows the GMII report from a

Data Sheet report:

All values displayed in nanoseconds (ns)

Setup/Hold to | clock gmii_tx_clk |

|

|

| ||

+ | + | + | ||||

| Setup to | Hold to | Clock | |||

Source | clk (edge) clk (edge) Internal Clock(s) | Phase | ||||

+ | + | + | ||||

gmii_tx_en | 1.531(R) | 0.000 | ||||

gmii_tx_er | 1.531(R) | 0.000 | ||||

gmii_txd<0> | 1.531(R) | 0.000 | ||||

gmii_txd<1> | 1.525(R) | 0.000 | ||||

gmii_txd<2> | 1.531(R) | 0.000 | ||||

gmii_txd<3> | 1.525(R) | 0.000 | ||||

gmii_txd<4> | 1.515(R) | 0.000 | ||||

gmii_txd<5> | 1.515(R) | 0.000 | ||||

gmii_txd<6> | 1.520(R) | 0.000 | ||||

gmii_txd<7> | 1.520(R) | 0.000 | ||||

+ | + | + | ||||

Virtex-4 or Virtex-5 Devices

Setup and hold results for the TBI or GMII input busses can be found in the data sheet report section of the Timing Report. Note that initially, the results do not indicate an obvious relationship to Figure

176 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |