Design Guidelines

R

Write an HDL Application

After reviewing the example design delivered with the core, write an HDL application that uses single or multiple instances of the block level module for the Ethernet

•Using the Ethernet

•Using the Ethernet

Synthesize your Design

Synthesize your entire design using the desired synthesis tool. The Ethernet

Create a Bitstream

Run the Xilinx tools map, par, and bitgen to create a bitstream that can be downloaded to a Xilinx device. The UCF produced by the CORE Generator should be used as the basis for the user UCF and care must be taken to constrain the design correctly. See Chapter 12, “Constraining the Core” for more information.

Simulate and Download your Design

After creating a bitstream that can be downloaded to a Xilinx device, simulate the entire design and download it to the desired device.

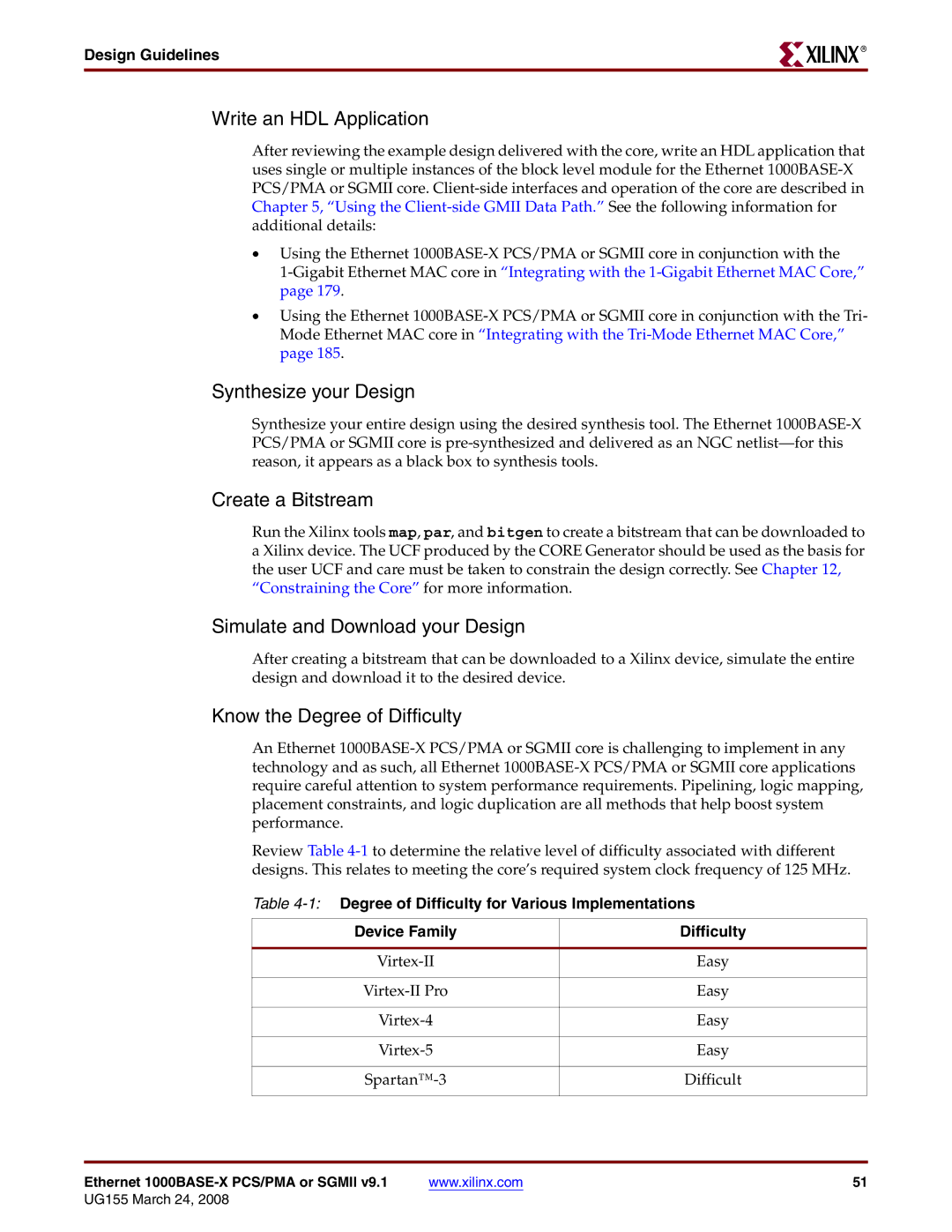

Know the Degree of Difficulty

An Ethernet

Review Table

Table

Device Family | Difficulty |

|

|

Easy | |

|

|

Easy | |

|

|

Easy | |

|

|

Easy | |

|

|

Difficult | |

|

|

Ethernet | www.xilinx.com | 51 |