R

Chapter 4: Designing with the Core

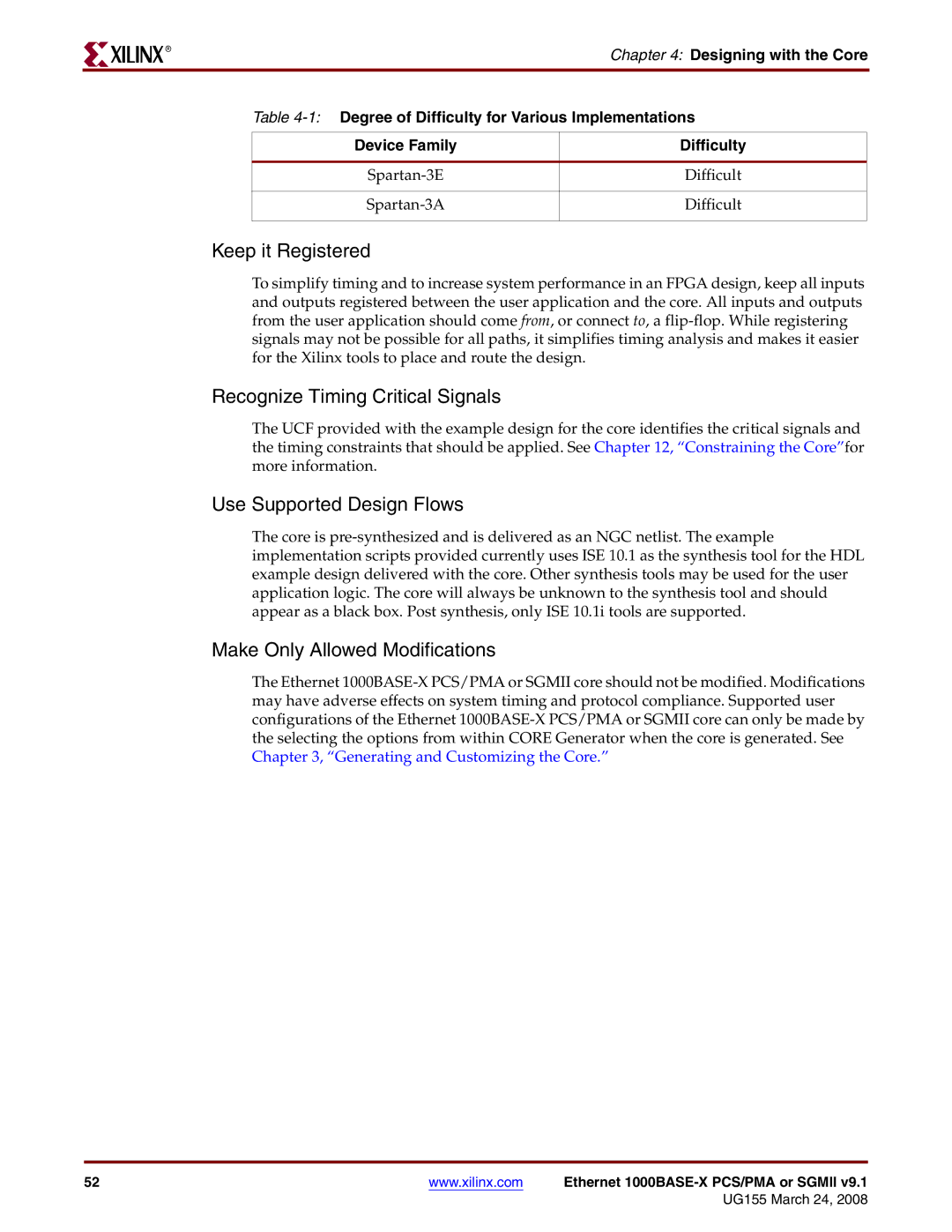

Table

Device Family | Difficulty |

|

|

Difficult | |

|

|

Difficult | |

|

|

Keep it Registered

To simplify timing and to increase system performance in an FPGA design, keep all inputs and outputs registered between the user application and the core. All inputs and outputs from the user application should come from, or connect to, a

Recognize Timing Critical Signals

The UCF provided with the example design for the core identifies the critical signals and the timing constraints that should be applied. See Chapter 12, “Constraining the Core”for more information.

Use Supported Design Flows

The core is

Make Only Allowed Modifications

The Ethernet

52 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |