R

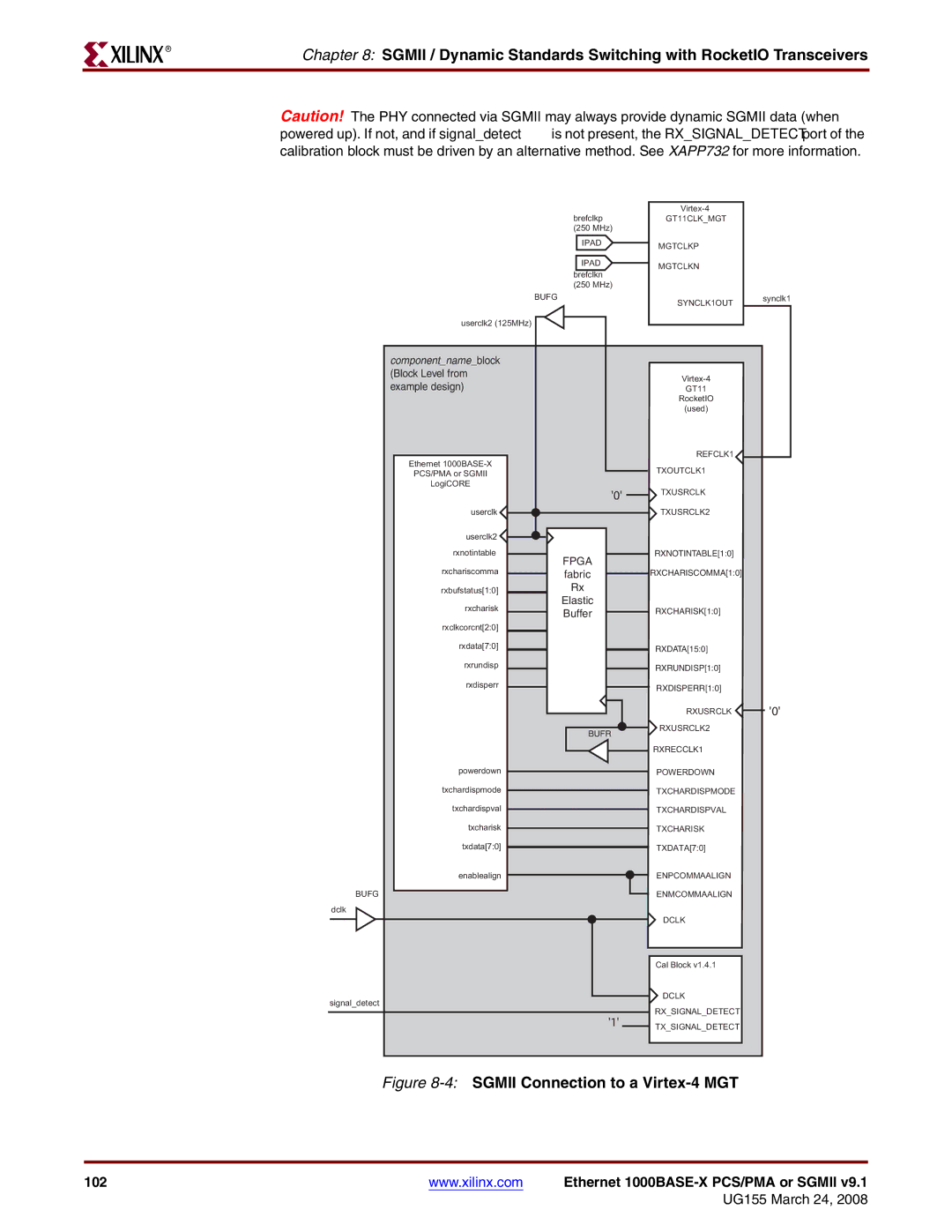

Chapter 8: SGMII / Dynamic Standards Switching with RocketIO Transceivers

Caution! The PHY connected via SGMII may always provide dynamic SGMII data (when powered up). If not, and if signal_detect is not present, the RX_SIGNAL_DETECT port of the calibration block must be driven by an alternative method. See XAPP732 for more information.

brefclkp |

| ||

| GT11CLK_MGT | ||

(250 MHz) |

|

| |

IPAD |

| MGTCLKP | |

| |||

|

|

| |

IPAD |

|

| MGTCLKN |

|

| ||

brefclkn |

| ||

|

| ||

(250 MHz) |

|

| |

BUFG |

| SYNCLK1OUT | |

|

|

| |

userclk2 (125MHz) |

|

| |

| component_name_block |

|

|

|

|

|

|

|

|

| ||

| (Block Level from |

|

|

|

|

|

|

| ||||

| example design) |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

| GT11 | ||||

|

|

|

|

|

|

|

|

|

|

| RocketIO | |

|

|

|

|

|

|

|

|

|

|

| (used) | |

|

|

|

|

|

|

|

|

|

|

| REFCLK1 | |

|

| Ethernet |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| TXOUTCLK1 | |||

|

| PCS/PMA or SGMII |

|

|

|

|

|

|

| |||

|

| LogiCORE | '0' |

| TXUSRCLK | |||||||

|

| userclk |

| |||||||||

|

|

|

|

|

|

|

|

| TXUSRCLK2 | |||

|

| userclk2 |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| ||

|

| rxnotintable |

| FPGA |

|

|

| RXNOTINTABLE[1:0] | ||||

|

| rxchariscomma |

|

|

|

|

|

| ||||

|

|

|

| fabric |

|

|

| RXCHARISCOMMA[1:0] | ||||

|

|

|

|

|

|

| ||||||

|

| rxbufstatus[1:0] |

|

|

| Rx |

|

|

|

| ||

|

| rxcharisk |

|

| Elastic |

|

|

|

| |||

|

|

|

| Buffer |

|

|

| RXCHARISK[1:0] | ||||

|

| rxclkcorcnt[2:0] |

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

| rxdata[7:0] |

|

|

|

|

|

|

|

| RXDATA[15:0] | |

|

|

|

|

|

|

|

|

|

| |||

|

| rxrundisp |

|

|

|

|

|

|

|

| RXRUNDISP[1:0] | |

|

|

|

|

|

|

|

|

|

| |||

|

| rxdisperr |

|

|

|

|

|

|

| RXDISPERR[1:0] | ||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| RXUSRCLK | |

|

|

|

|

|

| BUFR | RXUSRCLK2 |

| ||||

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

| |||||

|

| powerdown |

|

|

|

|

|

|

|

| RXRECCLK1 | |

|

|

|

|

|

|

|

|

|

| POWERDOWN | ||

|

|

|

|

|

|

|

|

|

| |||

|

| txchardispmode |

|

|

|

|

|

|

|

| TXCHARDISPMODE | |

|

|

|

|

|

|

|

|

|

| |||

|

| txchardispval |

|

|

|

|

|

|

|

| TXCHARDISPVAL | |

|

|

|

|

|

|

|

|

|

| |||

|

| txcharisk |

|

|

|

|

|

|

|

| TXCHARISK | |

|

|

|

|

|

|

|

|

|

| |||

|

| txdata[7:0] |

|

|

|

|

|

|

|

| TXDATA[7:0] | |

|

|

|

|

|

|

|

|

|

| |||

|

| enablealign |

|

|

|

|

|

|

| ENPCOMMAALIGN | ||

BUFG |

|

|

|

|

|

|

|

|

|

| ENMCOMMAALIGN | |

|

|

|

|

|

|

|

|

|

| |||

dclk |

|

|

|

|

|

|

|

|

|

| DCLK | |

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Cal Block v1.4.1 |

|

signal_detect |

|

|

|

|

|

|

|

|

|

| DCLK |

|

|

|

|

|

|

|

|

|

|

| RX_SIGNAL_DETECT |

| |

|

|

|

| '1' |

|

|

| |||||

|

|

|

|

|

| TX_SIGNAL_DETECT |

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

synclk1

'0'

Figure 8-4: SGMII Connection to a Virtex-4 MGT

102 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |