Required Constraints

R

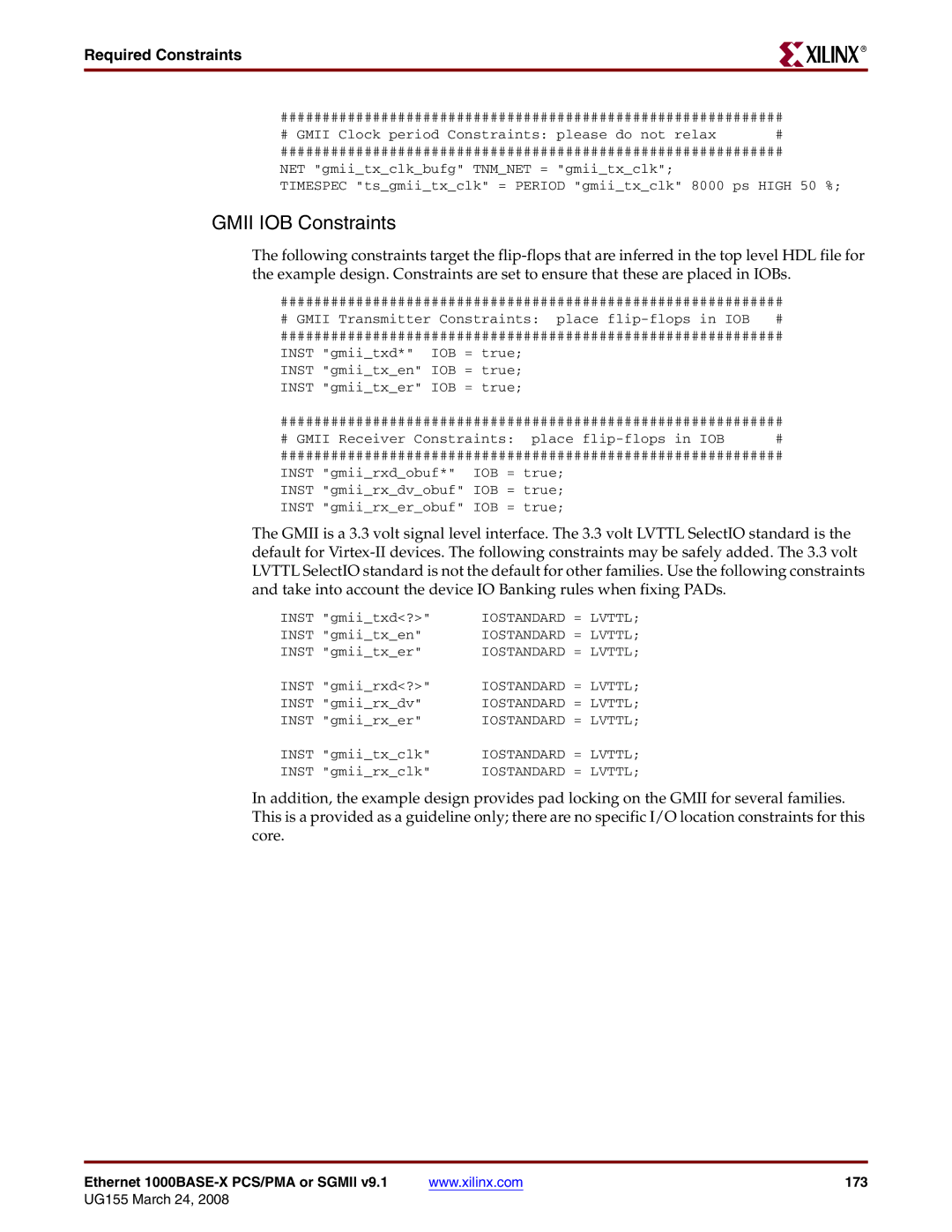

############################################################

# GMII Clock period Constraints: please do not relax | # |

############################################################

NET "gmii_tx_clk_bufg" TNM_NET = "gmii_tx_clk";

TIMESPEC "ts_gmii_tx_clk" = PERIOD "gmii_tx_clk" 8000 ps HIGH 50 %;

GMII IOB Constraints

The following constraints target the

############################################################

# GMII Transmitter Constraints: place

############################################################

INST "gmii_txd*" IOB = true; INST "gmii_tx_en" IOB = true; INST "gmii_tx_er" IOB = true;

############################################################

# GMII Receiver Constraints: place

############################################################

INST "gmii_rxd_obuf*" IOB = true; INST "gmii_rx_dv_obuf" IOB = true; INST "gmii_rx_er_obuf" IOB = true;

The GMII is a 3.3 volt signal level interface. The 3.3 volt LVTTL SelectIO standard is the default for

INST "gmii_txd<?>" | IOSTANDARD = LVTTL; |

INST "gmii_tx_en" | IOSTANDARD = LVTTL; |

INST "gmii_tx_er" | IOSTANDARD = LVTTL; |

INST "gmii_rxd<?>" | IOSTANDARD = LVTTL; |

INST "gmii_rx_dv" | IOSTANDARD = LVTTL; |

INST "gmii_rx_er" | IOSTANDARD = LVTTL; |

INST "gmii_tx_clk" | IOSTANDARD = LVTTL; |

INST "gmii_rx_clk" | IOSTANDARD = LVTTL; |

In addition, the example design provides pad locking on the GMII for several families. This is a provided as a guideline only; there are no specific I/O location constraints for this core.

Ethernet | www.xilinx.com | 173 |