R

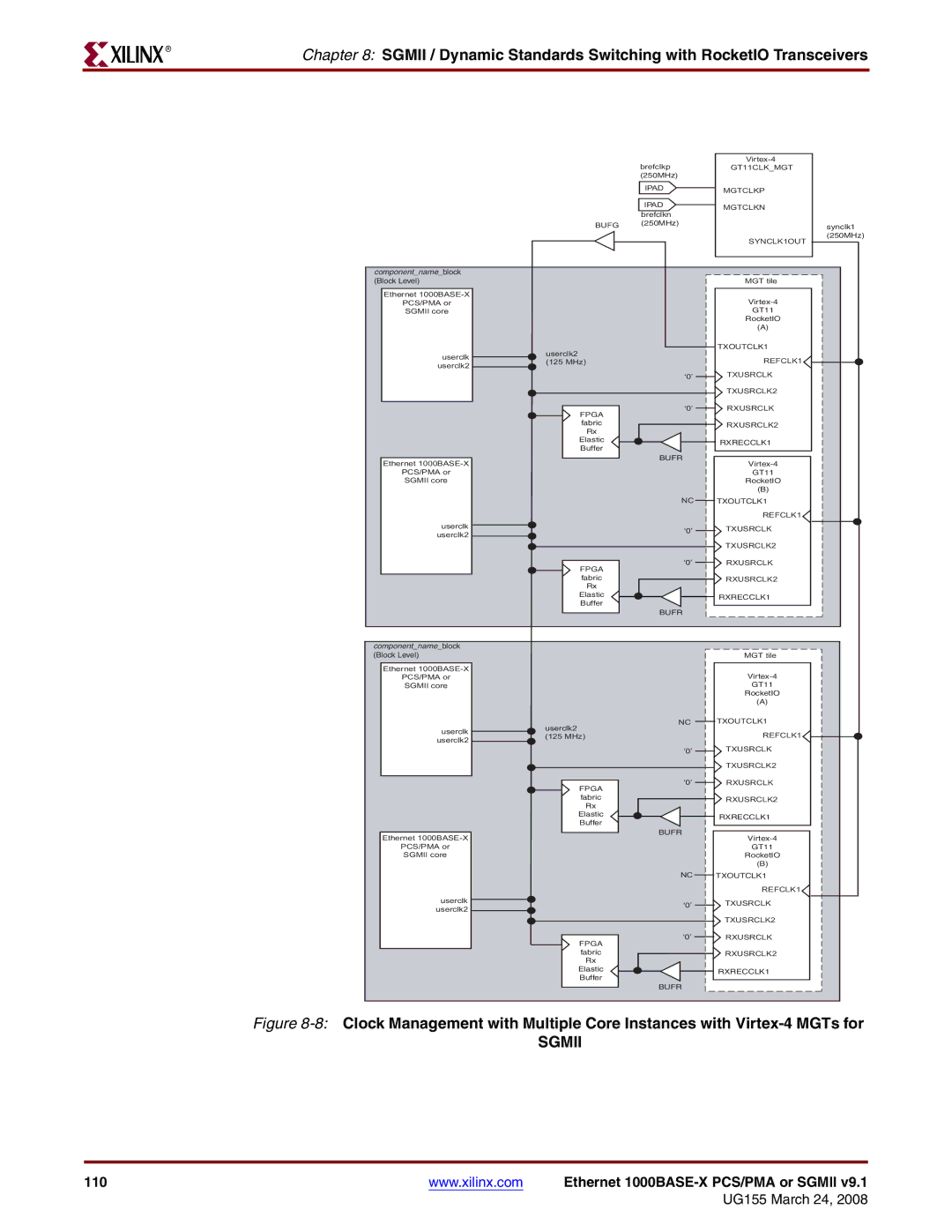

Chapter 8: SGMII / Dynamic Standards Switching with RocketIO Transceivers

|

|

| |

|

| brefclkp | GT11CLK_MGT |

|

| (250MHz) |

|

|

| IPAD | MGTCLKP |

|

|

| |

|

| IPAD | MGTCLKN |

|

| brefclkn | |

|

|

| |

| BUFG | (250MHz) | synclk1 |

|

|

| (250MHz) |

|

|

| SYNCLK1OUT |

component_name_block |

|

|

|

(Block Level) |

|

| MGT tile |

Ethernet |

|

| |

PCS/PMA or |

|

| |

SGMII core |

|

| GT11 |

|

|

| RocketIO |

|

|

| (A) |

| userclk2 |

| TXOUTCLK1 |

userclk |

| REFCLK1 | |

(125 MHz) |

| ||

userclk2 |

| ||

|

| TXUSRCLK | |

|

| ‘0’ | |

|

|

| TXUSRCLK2 |

| FPGA | ‘0’ | RXUSRCLK |

|

|

| |

| fabric |

| RXUSRCLK2 |

| Rx |

|

|

| Elastic |

| RXRECCLK1 |

| Buffer |

| |

|

|

| |

Ethernet |

| BUFR | |

|

| ||

PCS/PMA or |

|

| GT11 |

SGMII core |

|

| RocketIO |

|

|

| (B) |

|

| NC | TXOUTCLK1 |

|

|

| REFCLK1 |

userclk |

| ‘0’ | TXUSRCLK |

userclk2 |

| ||

|

|

| |

|

|

| TXUSRCLK2 |

| FPGA | ‘0’ | RXUSRCLK |

|

|

| |

| fabric |

| RXUSRCLK2 |

| Rx |

|

|

| Elastic |

| RXRECCLK1 |

| Buffer |

| |

|

|

| |

|

| BUFR |

|

component_name_block |

|

| |

(Block Level) |

| MGT tile | |

Ethernet |

| ||

PCS/PMA or |

| ||

SGMII core |

| GT11 | |

|

| RocketIO | |

|

| (A) | |

| NC | TXOUTCLK1 | |

userclk | userclk2 | REFCLK1 | |

(125 MHz) | |||

userclk2 | |||

| TXUSRCLK | ||

| ‘0’ | ||

|

| TXUSRCLK2 | |

| ‘0’ | RXUSRCLK | |

| FPGA |

| |

| fabric | RXUSRCLK2 | |

| Rx |

| |

| Elastic | RXRECCLK1 | |

| Buffer | ||

|

| ||

Ethernet | BUFR | ||

| |||

PCS/PMA or |

| GT11 | |

SGMII core |

| RocketIO | |

|

| (B) | |

| NC | TXOUTCLK1 | |

|

| REFCLK1 | |

userclk | ‘0’ | TXUSRCLK | |

userclk2 | |||

|

| ||

|

| TXUSRCLK2 | |

| ‘0’ | RXUSRCLK | |

| FPGA |

| |

| fabric | RXUSRCLK2 | |

| Rx |

| |

| Elastic | RXRECCLK1 | |

| Buffer | ||

|

| ||

| BUFR |

|

Figure 8-8: Clock Management with Multiple Core Instances with Virtex-4 MGTs for

SGMII

110 | www.xilinx.com | Ethernet |