R

Chapter 12: Constraining the Core

the HDL source code for the example design and with the information contained in Chapter 7,

Clock Period Constraints

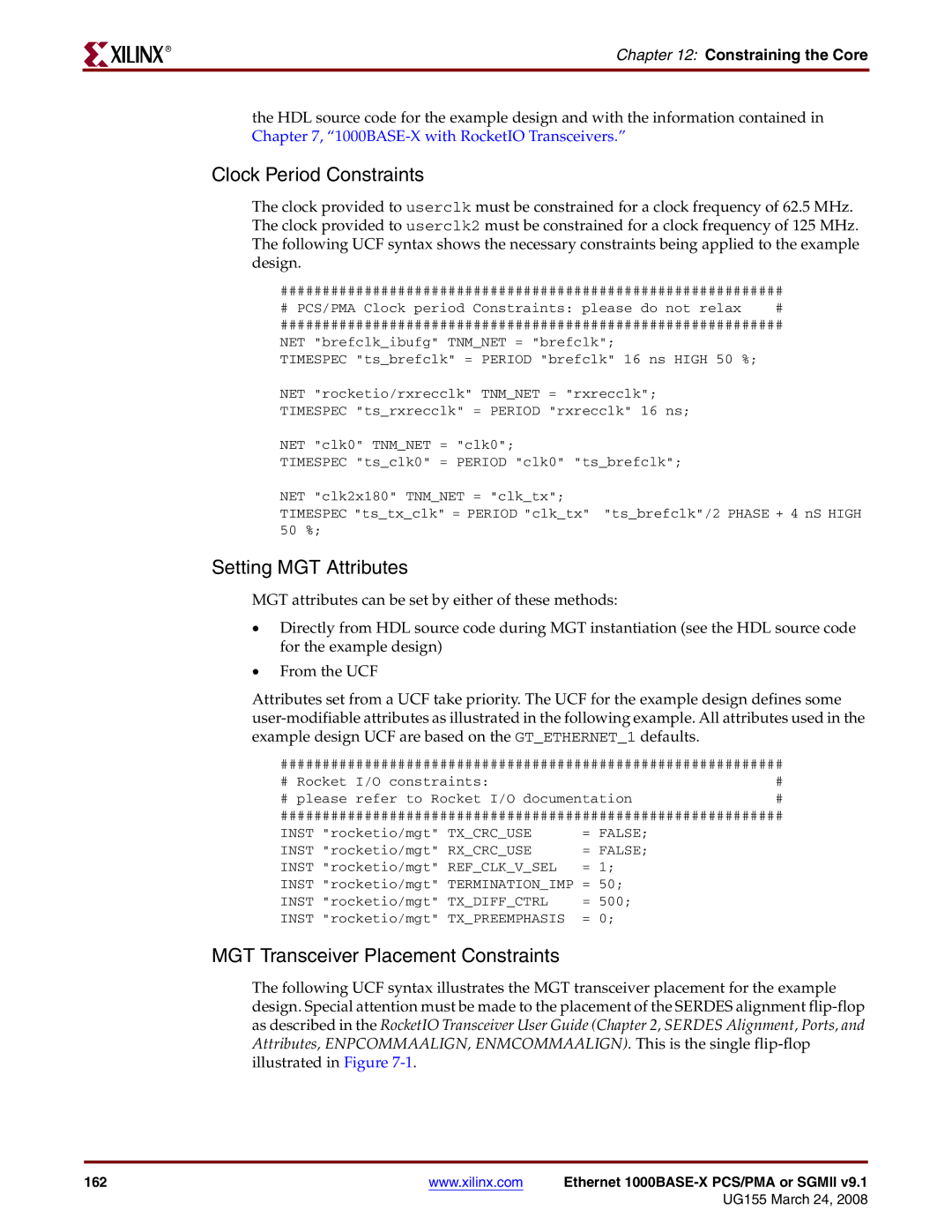

The clock provided to userclk must be constrained for a clock frequency of 62.5 MHz. The clock provided to userclk2 must be constrained for a clock frequency of 125 MHz. The following UCF syntax shows the necessary constraints being applied to the example design.

############################################################

# PCS/PMA Clock period Constraints: please do not relax #

############################################################

NET "brefclk_ibufg" TNM_NET = "brefclk";

TIMESPEC "ts_brefclk" = PERIOD "brefclk" 16 ns HIGH 50 %;

NET "rocketio/rxrecclk" TNM_NET = "rxrecclk";

TIMESPEC "ts_rxrecclk" = PERIOD "rxrecclk" 16 ns;

NET "clk0" TNM_NET = "clk0";

TIMESPEC "ts_clk0" = PERIOD "clk0" "ts_brefclk";

NET "clk2x180" TNM_NET = "clk_tx";

TIMESPEC "ts_tx_clk" = PERIOD "clk_tx" "ts_brefclk"/2 PHASE + 4 nS HIGH 50 %;

Setting MGT Attributes

MGT attributes can be set by either of these methods:

•Directly from HDL source code during MGT instantiation (see the HDL source code for the example design)

•From the UCF

Attributes set from a UCF take priority. The UCF for the example design defines some

############################################################

# | Rocket | I/O constraints: | # |

# | please | refer to Rocket I/O documentation | # |

############################################################

INST "rocketio/mgt" TX_CRC_USE | = FALSE; |

INST "rocketio/mgt" RX_CRC_USE | = FALSE; |

INST "rocketio/mgt" REF_CLK_V_SEL | = 1; |

INST "rocketio/mgt" TERMINATION_IMP | = 50; |

INST "rocketio/mgt" TX_DIFF_CTRL | = 500; |

INST "rocketio/mgt" TX_PREEMPHASIS | = 0; |

MGT Transceiver Placement Constraints

The following UCF syntax illustrates the MGT transceiver placement for the example design. Special attention must be made to the placement of the SERDES alignment

162 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |