R

Chapter 5: Using the Client-side GMII Data Path

False Carrier

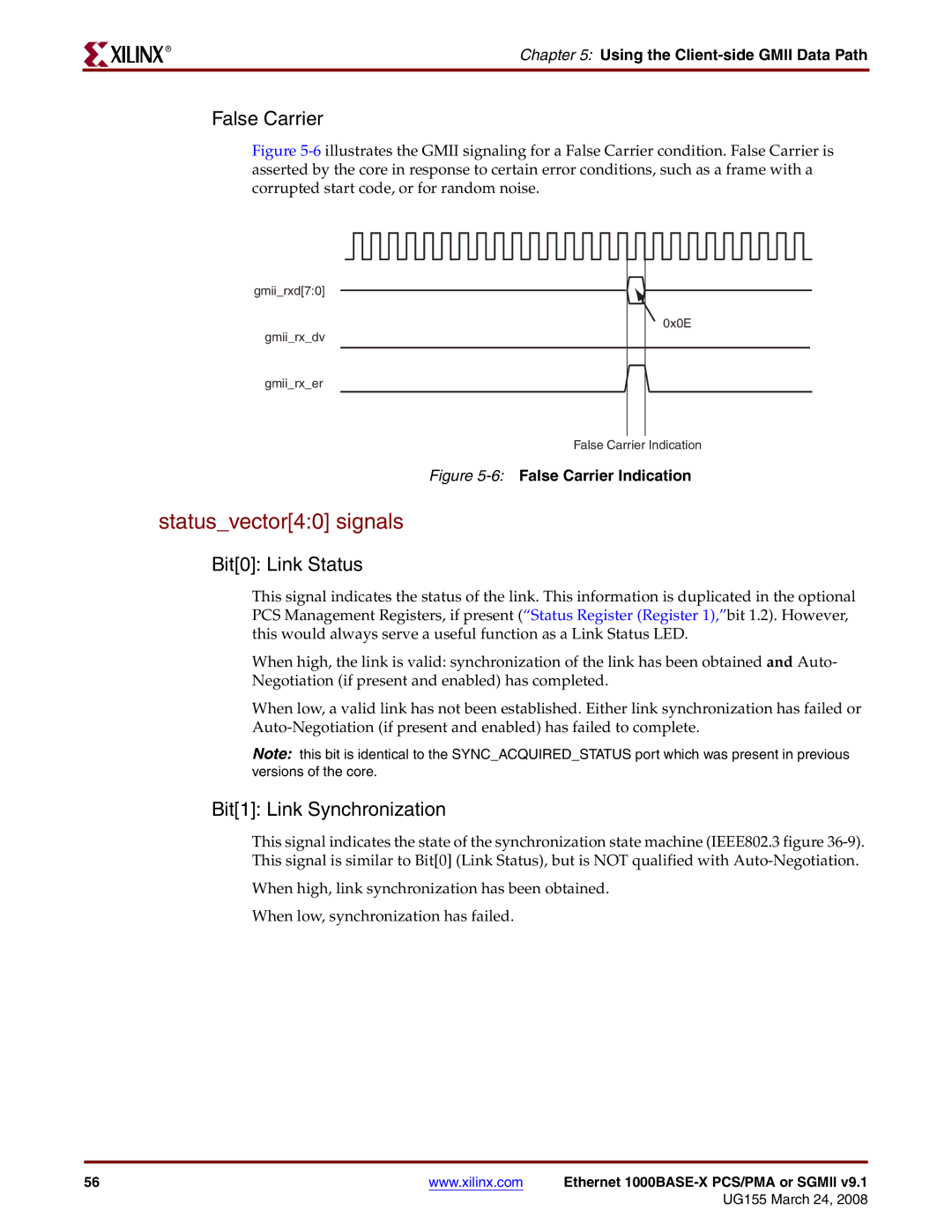

Figure 5-6 illustrates the GMII signaling for a False Carrier condition. False Carrier is asserted by the core in response to certain error conditions, such as a frame with a corrupted start code, or for random noise.

gmii_rxd[7:0]

0x0E

gmii_rx_dv

gmii_rx_er

False Carrier Indication

Figure 5-6: False Carrier Indication

status_vector[4:0] signals

Bit[0]: Link Status

This signal indicates the status of the link. This information is duplicated in the optional PCS Management Registers, if present (“Status Register (Register 1),”bit 1.2). However, this would always serve a useful function as a Link Status LED.

When high, the link is valid: synchronization of the link has been obtained and Auto-

Negotiation (if present and enabled) has completed.

When low, a valid link has not been established. Either link synchronization has failed or

Note: this bit is identical to the SYNC_ACQUIRED_STATUS port which was present in previous versions of the core.

Bit[1]: Link Synchronization

This signal indicates the state of the synchronization state machine (IEEE802.3 figure

When high, link synchronization has been obtained.

When low, synchronization has failed.

56 | www.xilinx.com | Ethernet |

|

| UG155 March 24, 2008 |