Management Registers

R

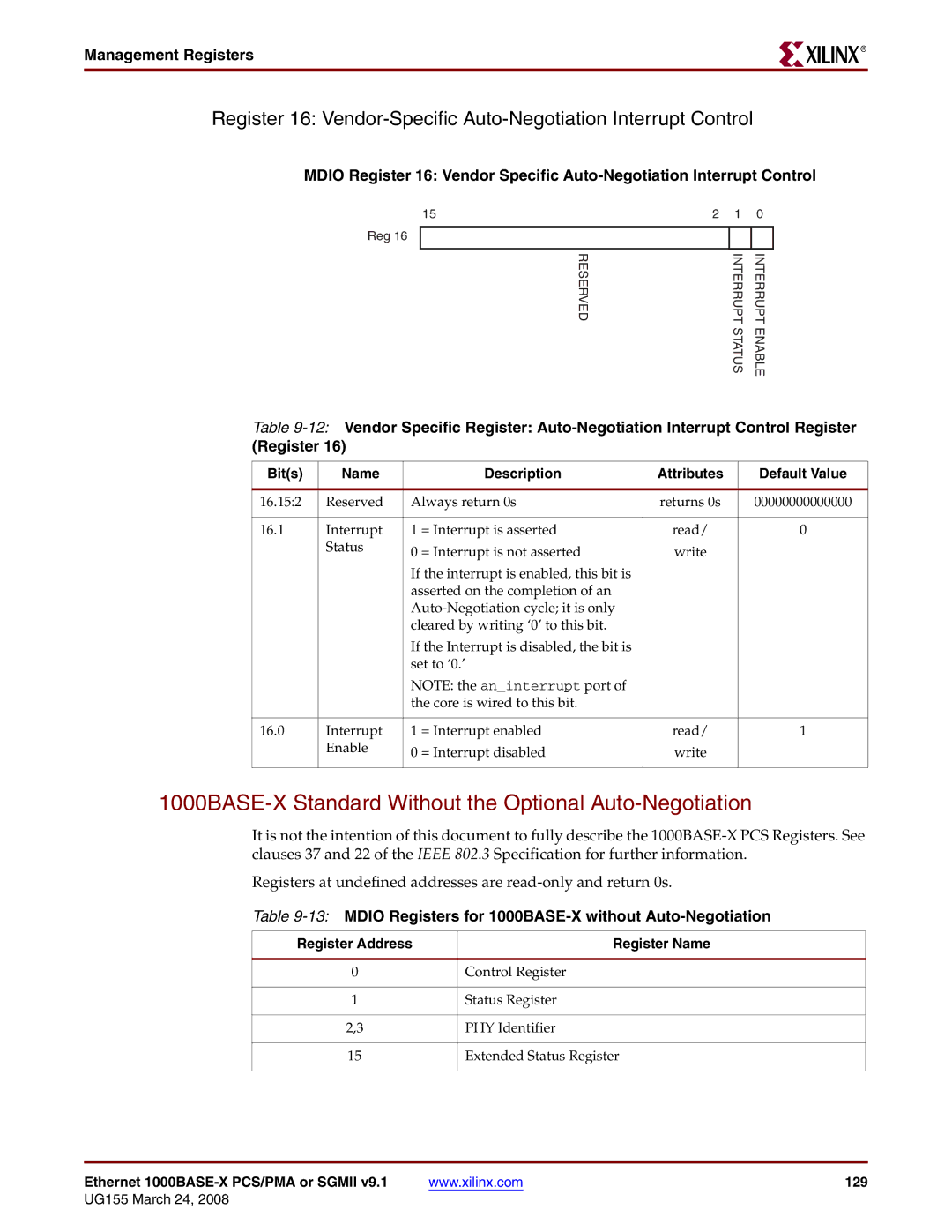

Register 16:

MDIO Register 16: Vendor Specific

15 | 2 | 1 | 0 | |

Reg 16 |

|

|

|

|

|

|

|

| |

|

|

|

|

|

| RESERVED |

| INTERRUPT | INTERRUPT |

|

|

| STATUS | ENABLE |

Table

Bit(s) | Name |

| Description | Attributes | Default Value |

|

|

|

|

| |

16.15:2 | Reserved | Always return 0s | returns 0s | 00000000000000 | |

|

|

|

|

|

|

16.1 | Interrupt | 1 | = Interrupt is asserted | read/ | 0 |

| Status | 0 | = Interrupt is not asserted | write |

|

|

|

| |||

|

| If the interrupt is enabled, this bit is |

|

| |

|

| asserted on the completion of an |

|

| |

|

|

|

| ||

|

| cleared by writing ‘0’ to this bit. |

|

| |

|

| If the Interrupt is disabled, the bit is |

|

| |

|

| set to ‘0.’ |

|

| |

|

| NOTE: the an_interrupt port of |

|

| |

|

| the core is wired to this bit. |

|

| |

|

|

|

|

|

|

16.0 | Interrupt | 1 | = Interrupt enabled | read/ | 1 |

| Enable | 0 | = Interrupt disabled | write |

|

|

|

| |||

|

|

|

|

|

|

1000BASE-X Standard Without the Optional Auto-Negotiation

It is not the intention of this document to fully describe the

Registers at undefined addresses are

Table 9-13: MDIO Registers for 1000BASE-X without Auto-Negotiation

Register Address | Register Name |

|

|

0 | Control Register |

|

|

1 | Status Register |

|

|

2,3 | PHY Identifier |

|

|

15 | Extended Status Register |

|

|

Ethernet | www.xilinx.com | 129 |