Management Registers

Table 9-14: Control Register (Register 0) (Continued)

R

Bit(s) | Name | Description | Attributes | Default | |

Value | |||||

|

|

|

| ||

|

|

|

|

| |

0.9 | Restart Auto- | Ignore this bit because | read/ write | 0 | |

| Negotiation | is not included. |

|

| |

|

|

|

|

| |

0.8 | Duplex Mode | Always returns a ‘1’ for this bit to signal | returns 1 | 1 | |

|

|

|

| ||

|

|

|

|

| |

0.7 | Collision Test | Always returns a ‘0’ for this bit to disable | returns 0 | 0 | |

|

| COL test. |

|

| |

|

|

|

|

| |

0.6 | Speed | Always returns a ‘1’ for this bit. Together | returns 1 | 1 | |

| Selection(MS | with bit 0.13, speed selection of 1000 |

|

| |

| B) | Mbps is identified |

|

| |

|

|

|

|

| |

0.5 | Unidirectiona | Ignore this bit because | read/ write | 0 | |

| l Enable | is not included. |

|

| |

|

|

|

|

| |

0.4:0 | Reserved | Always return 0s , writes ignored. | returns 0s | 00000 | |

|

|

|

|

|

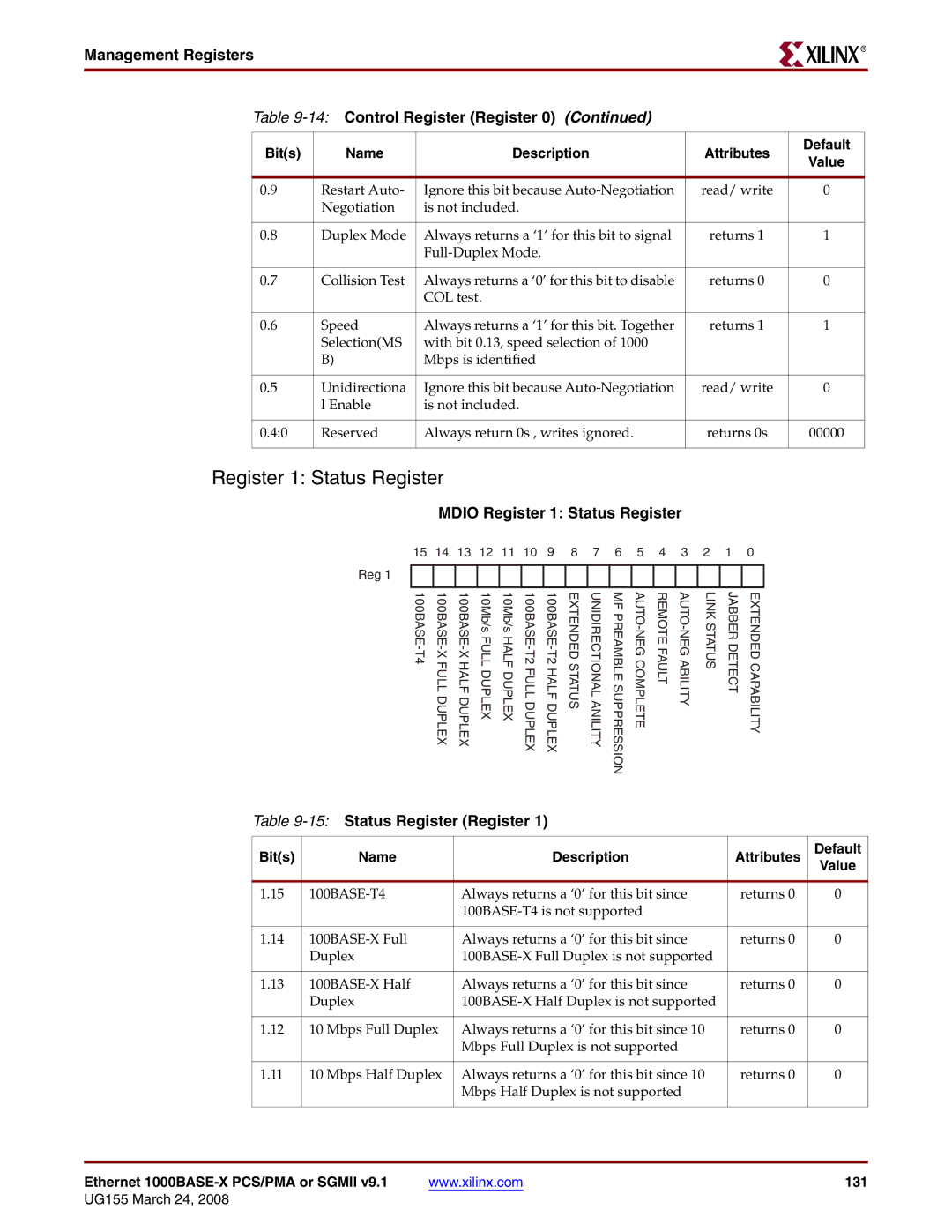

Register 1: Status Register

MDIO Register 1: Status Register

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Reg 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10Mb/s FULL DUPLEX | 10Mb/s HALF DUPLEX | EXTENDED STATUS | UNIDIRECTIONAL ANILITY | MF PREAMBLE SUPPRESSION | REMOTE FAULT | LINK STATUS | JABBER DETECT | EXTENDED CAPABILITY | |||||||

Table 9-15: Status Register (Register 1)

Bit(s) | Name | Description | Attributes | Default |

|

|

|

| Value |

1.15 | Always returns a ‘0’ for this bit since | returns 0 | 0 | |

|

|

|

| |

|

|

|

|

|

1.14 | Always returns a ‘0’ for this bit since | returns 0 | 0 | |

| Duplex |

|

| |

|

|

|

|

|

1.13 | Always returns a ‘0’ for this bit since | returns 0 | 0 | |

| Duplex |

|

| |

|

|

|

|

|

1.12 | 10 Mbps Full Duplex | Always returns a ‘0’ for this bit since 10 | returns 0 | 0 |

|

| Mbps Full Duplex is not supported |

|

|

|

|

|

|

|

1.11 | 10 Mbps Half Duplex | Always returns a ‘0’ for this bit since 10 | returns 0 | 0 |

|

| Mbps Half Duplex is not supported |

|

|

|

|

|

|

|

Ethernet | www.xilinx.com | 131 |