Required Constraints

R

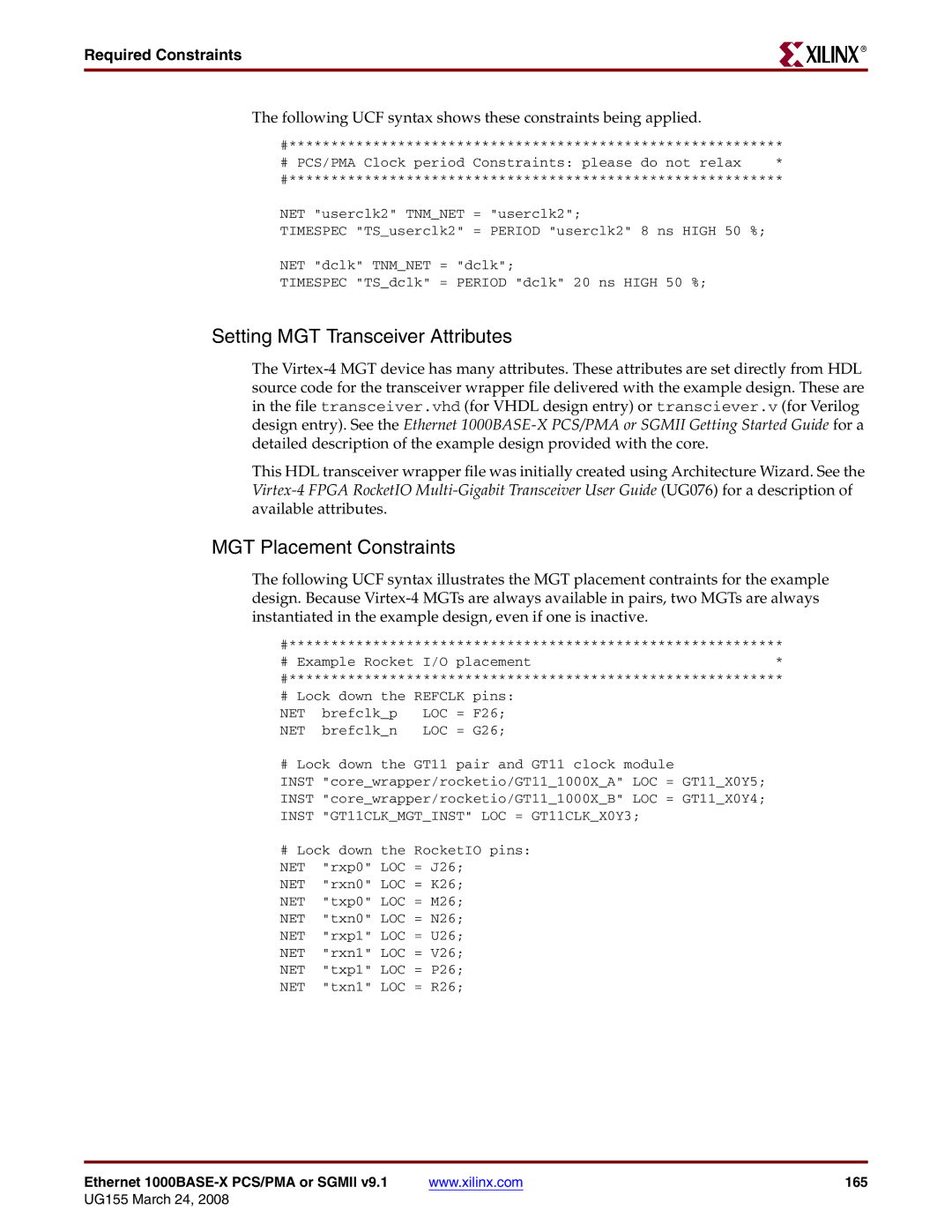

The following UCF syntax shows these constraints being applied.

#***********************************************************

# PCS/PMA Clock period Constraints: please do not relax * #***********************************************************

NET "userclk2" TNM_NET = "userclk2";

TIMESPEC "TS_userclk2" = PERIOD "userclk2" 8 ns HIGH 50 %;

NET "dclk" TNM_NET = "dclk";

TIMESPEC "TS_dclk" = PERIOD "dclk" 20 ns HIGH 50 %;

Setting MGT Transceiver Attributes

The

This HDL transceiver wrapper file was initially created using Architecture Wizard. See the

MGT Placement Constraints

The following UCF syntax illustrates the MGT placement contraints for the example design. Because

#***********************************************************

# Example Rocket I/O placement* #***********************************************************

# Lock down the REFCLK pins:

NET | brefclk_p | LOC | = | F26; |

NET | brefclk_n | LOC | = | G26; |

# Lock down the GT11 pair and GT11 clock module

INST "core_wrapper/rocketio/GT11_1000X_A" LOC = GT11_X0Y5; INST "core_wrapper/rocketio/GT11_1000X_B" LOC = GT11_X0Y4; INST "GT11CLK_MGT_INST" LOC = GT11CLK_X0Y3;

#Lock down the RocketIO pins: NET "rxp0" LOC = J26;

NET "rxn0" LOC = K26; NET "txp0" LOC = M26; NET "txn0" LOC = N26; NET "rxp1" LOC = U26; NET "rxn1" LOC = V26; NET "txp1" LOC = P26; NET "txn1" LOC = R26;

Ethernet | www.xilinx.com | 165 |