Rx Elastic Buffers: Depths and Maximum Frame Sizes

Table

Standard / Speed | Maximum Frame Size |

|

|

280000 | |

|

|

SGMII (1 Gbps) | 280000 |

|

|

SGMII (100 Mbps) | 28000 |

|

|

SGMII (10 Mbps) | 2800 |

|

|

TBI Rx Elastic Buffer

For SGMII / Dynamic Switching

R

The Rx Elastic Buffer used for the SGMII or Dynamic Standards Switching is identical to the method use in “SGMII Fabric Rx Elastic Buffer.”

For 1000BASE-X

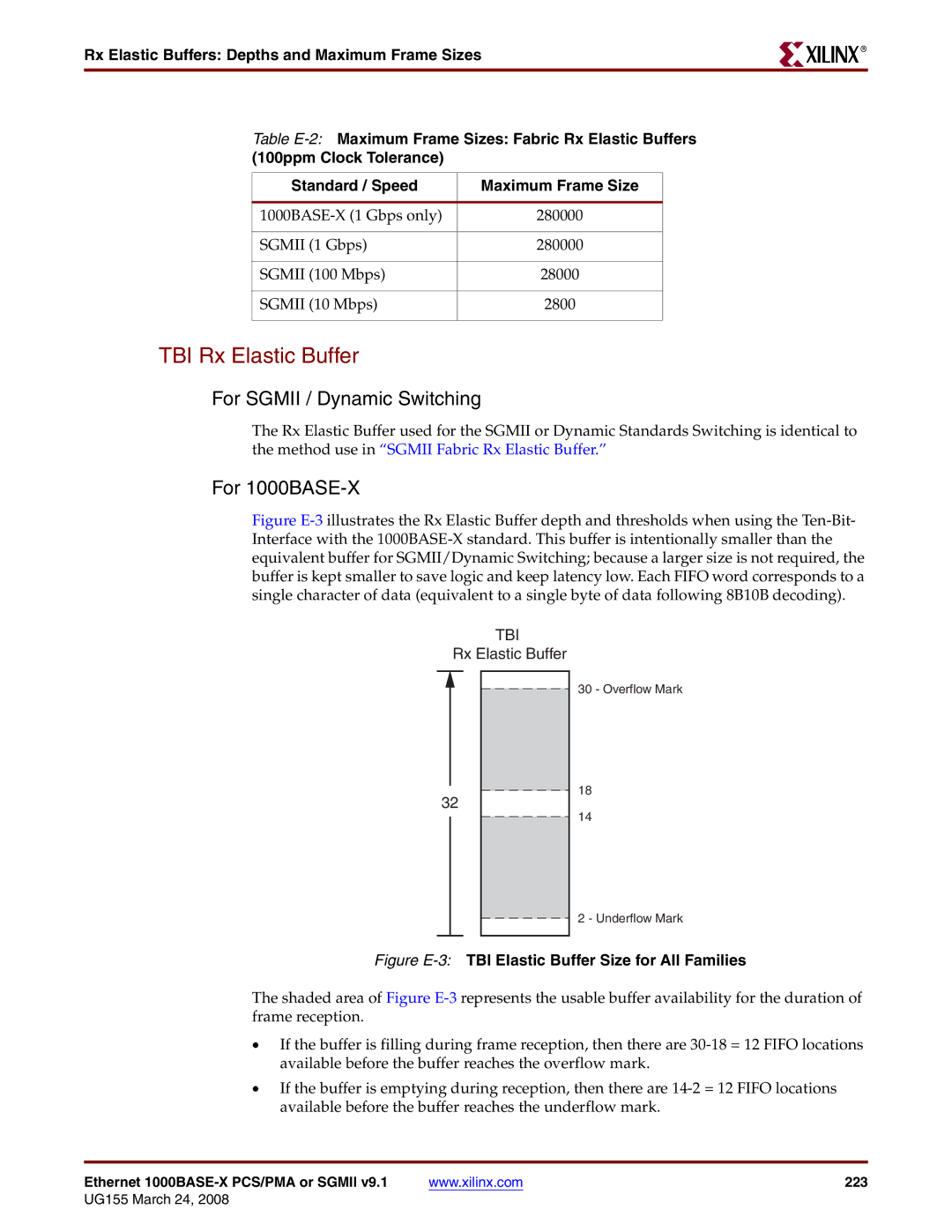

Figure E-3 illustrates the Rx Elastic Buffer depth and thresholds when using the Ten-Bit- Interface with the 1000BASE-X standard. This buffer is intentionally smaller than the equivalent buffer for SGMII/Dynamic Switching; because a larger size is not required, the buffer is kept smaller to save logic and keep latency low. Each FIFO word corresponds to a single character of data (equivalent to a single byte of data following 8B10B decoding).

TBI

Rx Elastic Buffer

30 - Overflow Mark

32

18

14

2 - Underflow Mark

Figure E-3: TBI Elastic Buffer Size for All Families

The shaded area of Figure

•If the buffer is filling during frame reception, then there are

•If the buffer is emptying during reception, then there are

Ethernet | www.xilinx.com | 223 |