Optional Configuration Vector

R

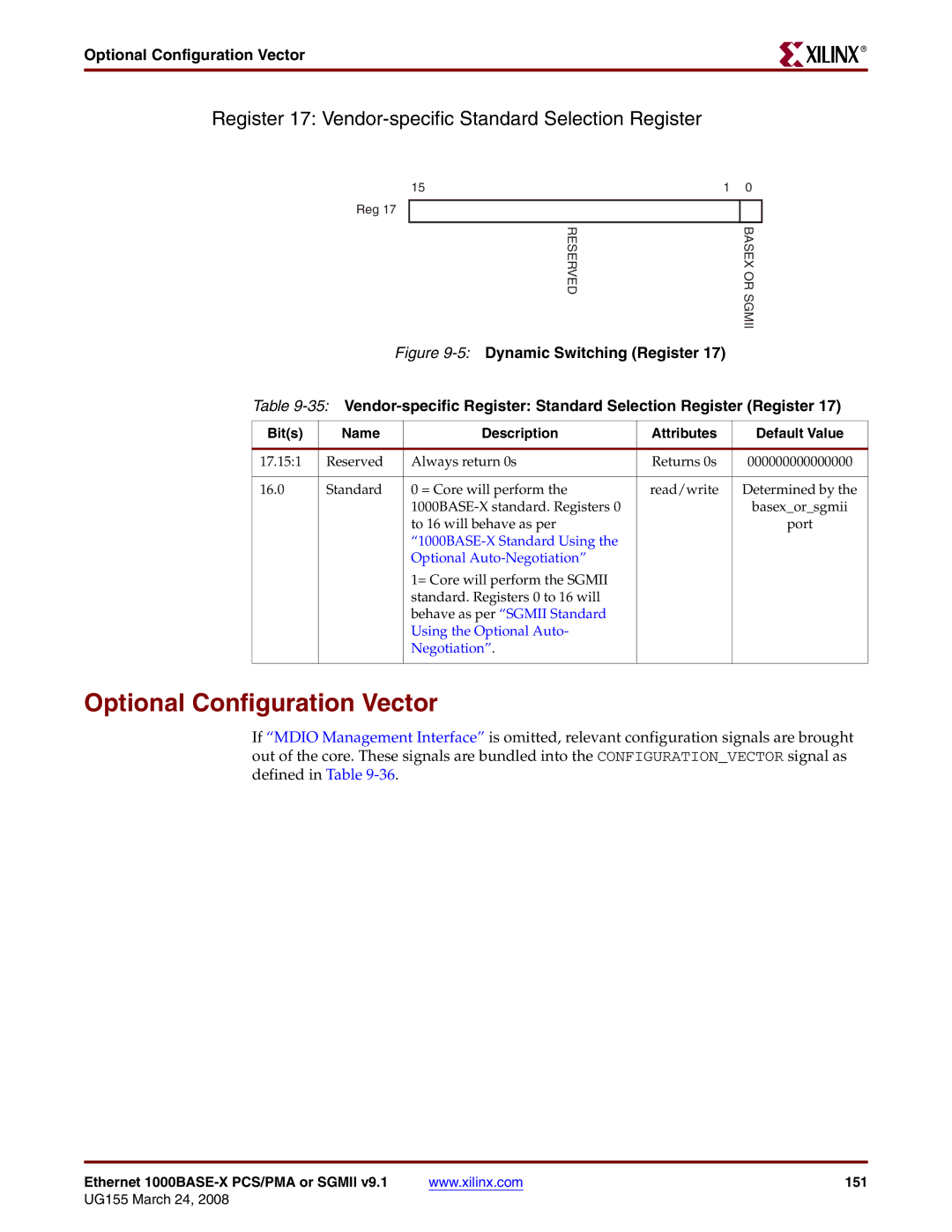

Register 17: Vendor-specific Standard Selection Register

|

| 15 | 1 | 0 |

| |||

| Reg 17 |

|

|

|

|

| ||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| RESERVED |

|

| BASEX OR SGMII | |

|

| Figure |

|

|

| |||

Table | ||||||||

|

|

|

|

|

|

|

|

|

Bit(s) | Name |

|

| Description | Attributes |

| Default Value | |

|

|

|

|

|

|

|

|

|

17.15:1 | Reserved |

|

| Always return 0s | Returns 0s | 000000000000000 | ||

|

|

|

|

|

|

|

|

|

16.0 | Standard |

|

| 0 = Core will perform the | read/write |

| Determined by the | |

|

|

|

|

|

| basex_or_sgmii | ||

|

|

|

| to 16 will behave as per |

|

|

| port |

|

|

|

|

|

|

|

| |

|

|

|

| Optional |

|

|

|

|

|

|

|

| 1= Core will perform the SGMII |

|

|

|

|

|

|

|

| standard. Registers 0 to 16 will |

|

|

|

|

|

|

|

| behave as per “SGMII Standard |

|

|

|

|

|

|

|

| Using the Optional Auto- |

|

|

|

|

|

|

|

| Negotiation”. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Configuration Vector

If “MDIO Management Interface” is omitted, relevant configuration signals are brought out of the core. These signals are bundled into the CONFIGURATION_VECTOR signal as defined in Table

Ethernet | www.xilinx.com | 151 |