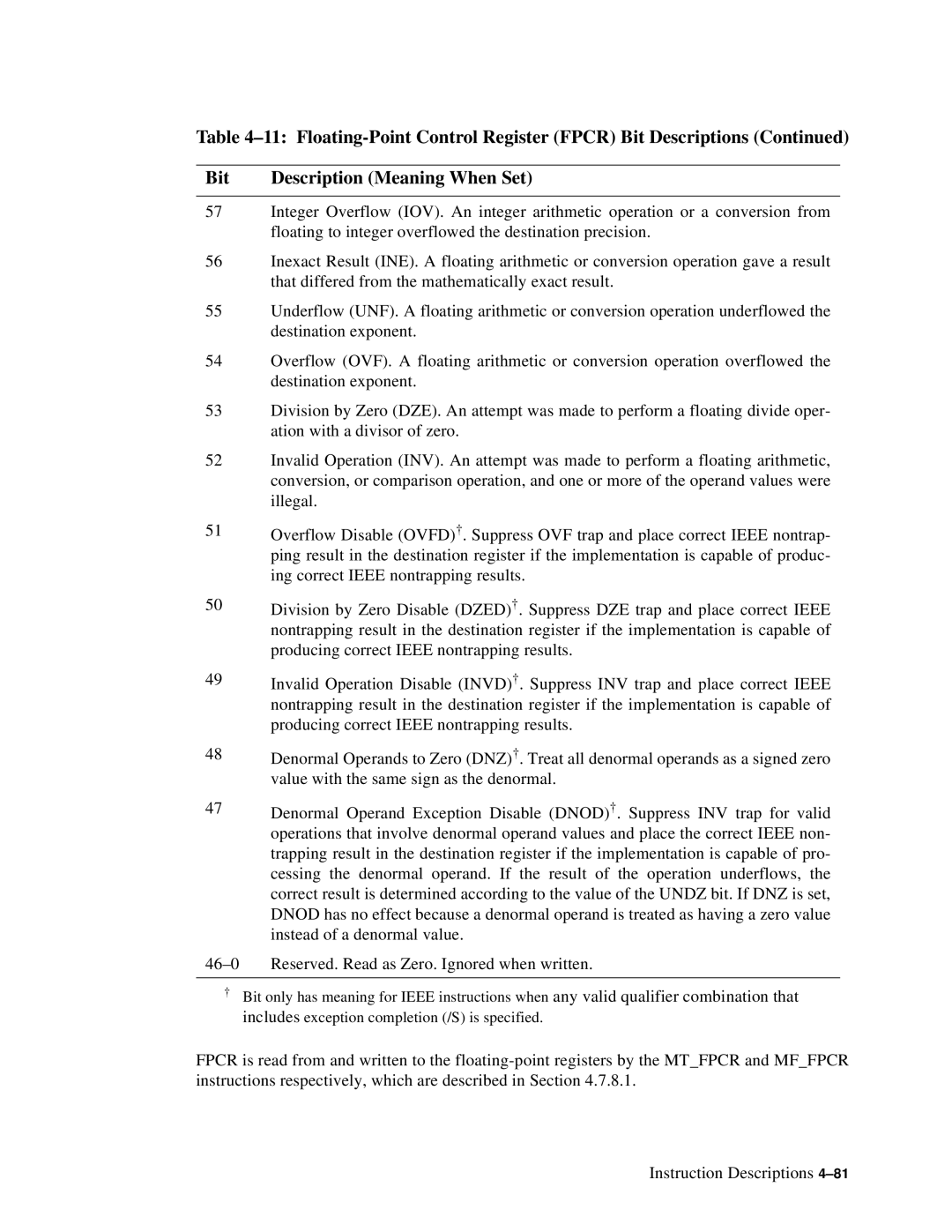

Table

Bit | Description (Meaning When Set) |

57Integer Overflow (IOV). An integer arithmetic operation or a conversion from floating to integer overflowed the destination precision.

56Inexact Result (INE). A floating arithmetic or conversion operation gave a result that differed from the mathematically exact result.

55Underflow (UNF). A floating arithmetic or conversion operation underflowed the destination exponent.

54Overflow (OVF). A floating arithmetic or conversion operation overflowed the destination exponent.

53Division by Zero (DZE). An attempt was made to perform a floating divide oper- ation with a divisor of zero.

52Invalid Operation (INV). An attempt was made to perform a floating arithmetic, conversion, or comparison operation, and one or more of the operand values were illegal.

51Overflow Disable (OVFD)† . Suppress OVF trap and place correct IEEE nontrap- ping result in the destination register if the implementation is capable of produc- ing correct IEEE nontrapping results.

50Division by Zero Disable (DZED)† . Suppress DZE trap and place correct IEEE nontrapping result in the destination register if the implementation is capable of producing correct IEEE nontrapping results.

49Invalid Operation Disable (INVD)† . Suppress INV trap and place correct IEEE nontrapping result in the destination register if the implementation is capable of producing correct IEEE nontrapping results.

48Denormal Operands to Zero (DNZ)† . Treat all denormal operands as a signed zero value with the same sign as the denormal.

47Denormal Operand Exception Disable (DNOD)† . Suppress INV trap for valid operations that involve denormal operand values and place the correct IEEE non- trapping result in the destination register if the implementation is capable of pro- cessing the denormal operand. If the result of the operation underflows, the correct result is determined according to the value of the UNDZ bit. If DNZ is set, DNOD has no effect because a denormal operand is treated as having a zero value instead of a denormal value.

†Bit only has meaning for IEEE instructions when any valid qualifier combination that includes exception completion (/S) is specified.

FPCR is read from and written to the

Instruction Descriptions