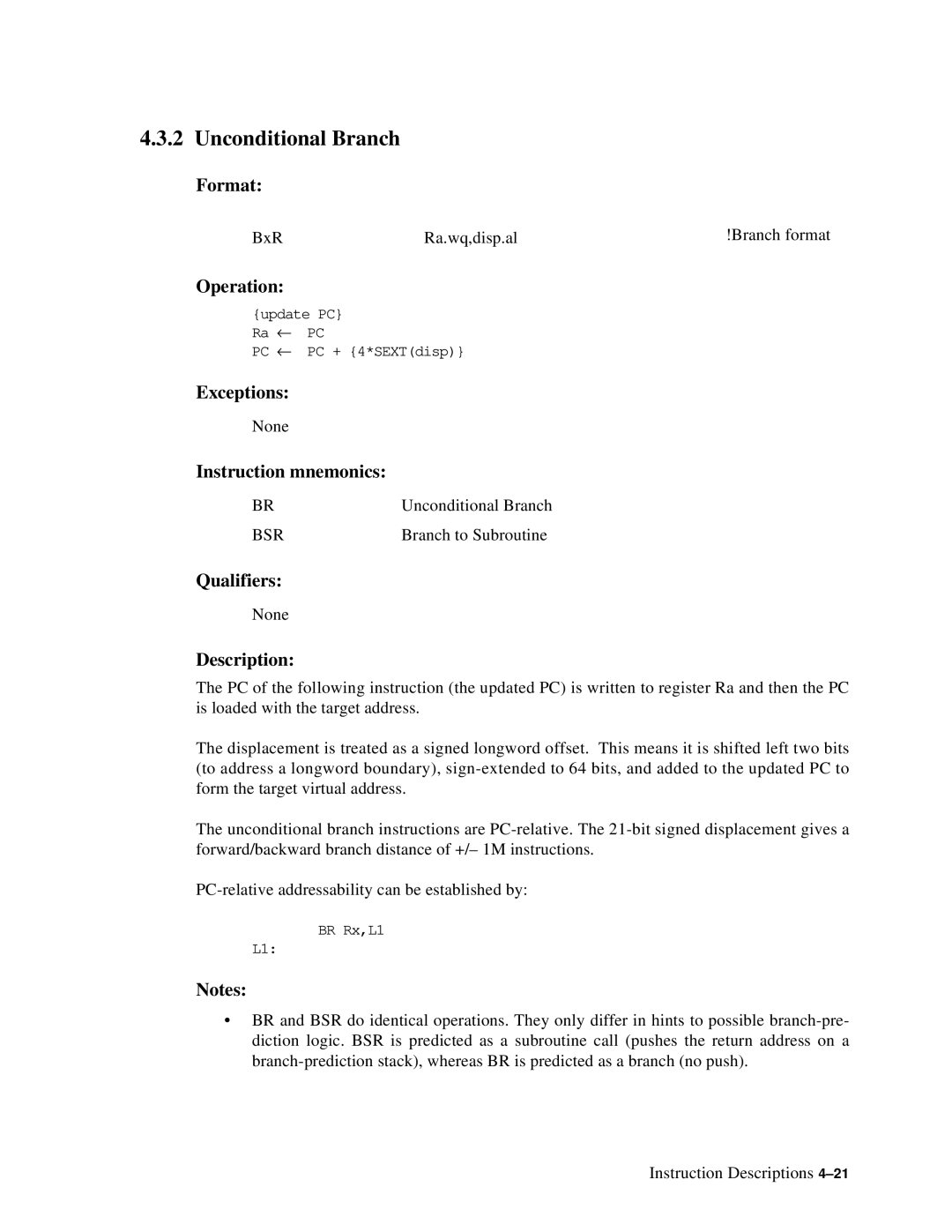

4.3.2 Unconditional Branch

Format:

BxRRa.wq,disp.al!Branch format

Operation:

{update PC} Ra ← PC

PC ← PC + {4*SEXT(disp)}

Exceptions: |

|

None |

|

Instruction mnemonics: |

|

BR | Unconditional Branch |

BSR | Branch to Subroutine |

Qualifiers: |

|

None |

|

Description:

The PC of the following instruction (the updated PC) is written to register Ra and then the PC is loaded with the target address.

The displacement is treated as a signed longword offset. This means it is shifted left two bits (to address a longword boundary),

The unconditional branch instructions are

BR Rx,L1

L1:

Notes:

•BR and BSR do identical operations. They only differ in hints to possible

Instruction Descriptions