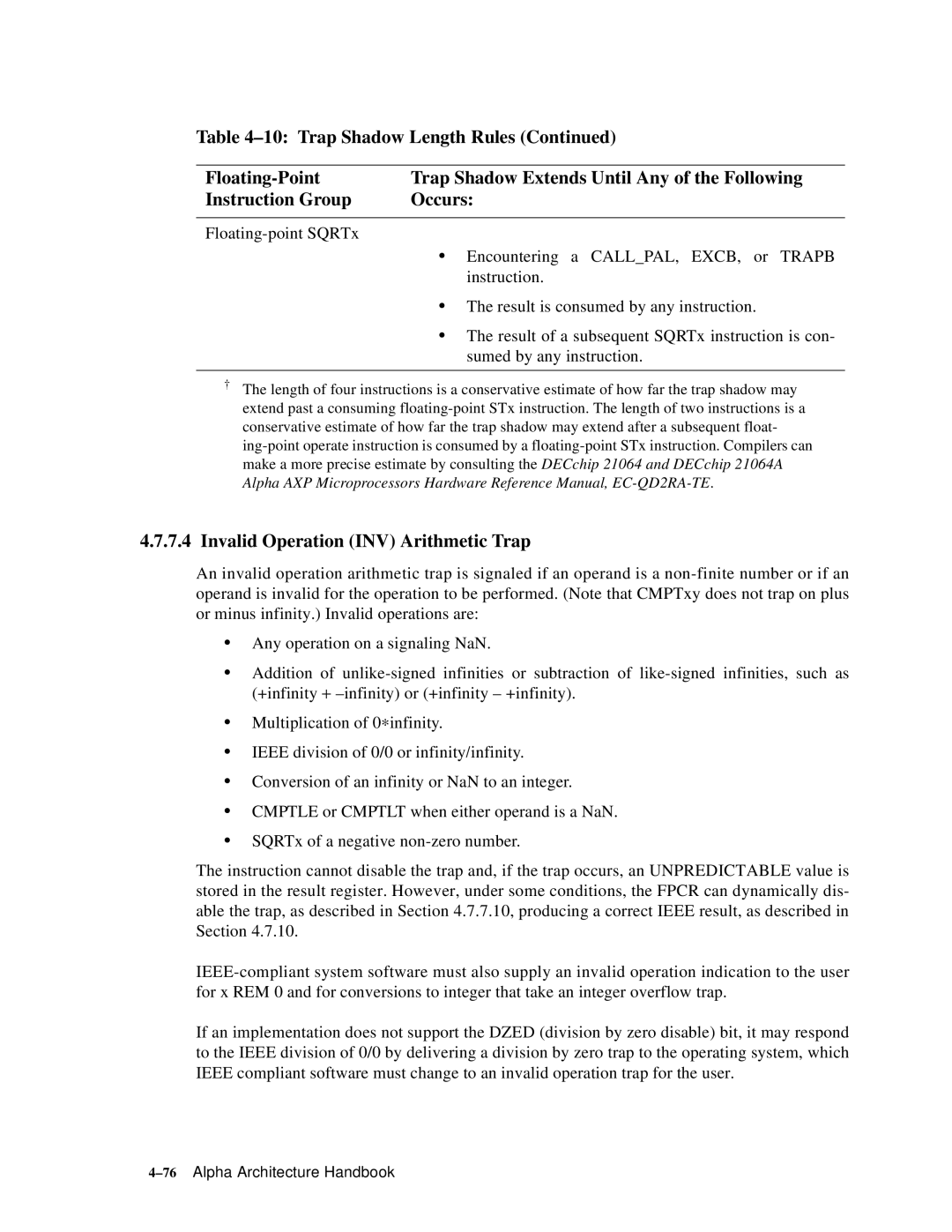

Table

Trap Shadow Extends Until Any of the Following | |

Instruction Group | Occurs: |

•Encountering a CALL_PAL, EXCB, or TRAPB instruction.

•The result is consumed by any instruction.

•The result of a subsequent SQRTx instruction is con- sumed by any instruction.

†The length of four instructions is a conservative estimate of how far the trap shadow may extend past a consuming

4.7.7.4Invalid Operation (INV) Arithmetic Trap

An invalid operation arithmetic trap is signaled if an operand is a

•Any operation on a signaling NaN.

•Addition of

•Multiplication of 0∗infinity.

•IEEE division of 0/0 or infinity/infinity.

•Conversion of an infinity or NaN to an integer.

•CMPTLE or CMPTLT when either operand is a NaN.

•SQRTx of a negative

The instruction cannot disable the trap and, if the trap occurs, an UNPREDICTABLE value is stored in the result register. However, under some conditions, the FPCR can dynamically dis- able the trap, as described in Section 4.7.7.10, producing a correct IEEE result, as described in Section 4.7.10.

If an implementation does not support the DZED (division by zero disable) bit, it may respond to the IEEE division of 0/0 by delivering a division by zero trap to the operating system, which IEEE compliant software must change to an invalid operation trap for the user.