Compaq software may choose to initialize the software status bits and the trap disable bits to all 1’s to avoid any initial trapping when an exception condition first occurs. Or, software may choose to initialize those bits to all 0’s in order to provide a summary of the exception behavior when the program terminates.

In any event, the exception bits in the FPCR are still useful to programs. A program can clear all of the exception bits in the FPCR, execute a single

3.Because of the way the LDS and STS instructions manipulate bits <61:59> of float-

4.7.9Floating-Point Instruction Function Field Format

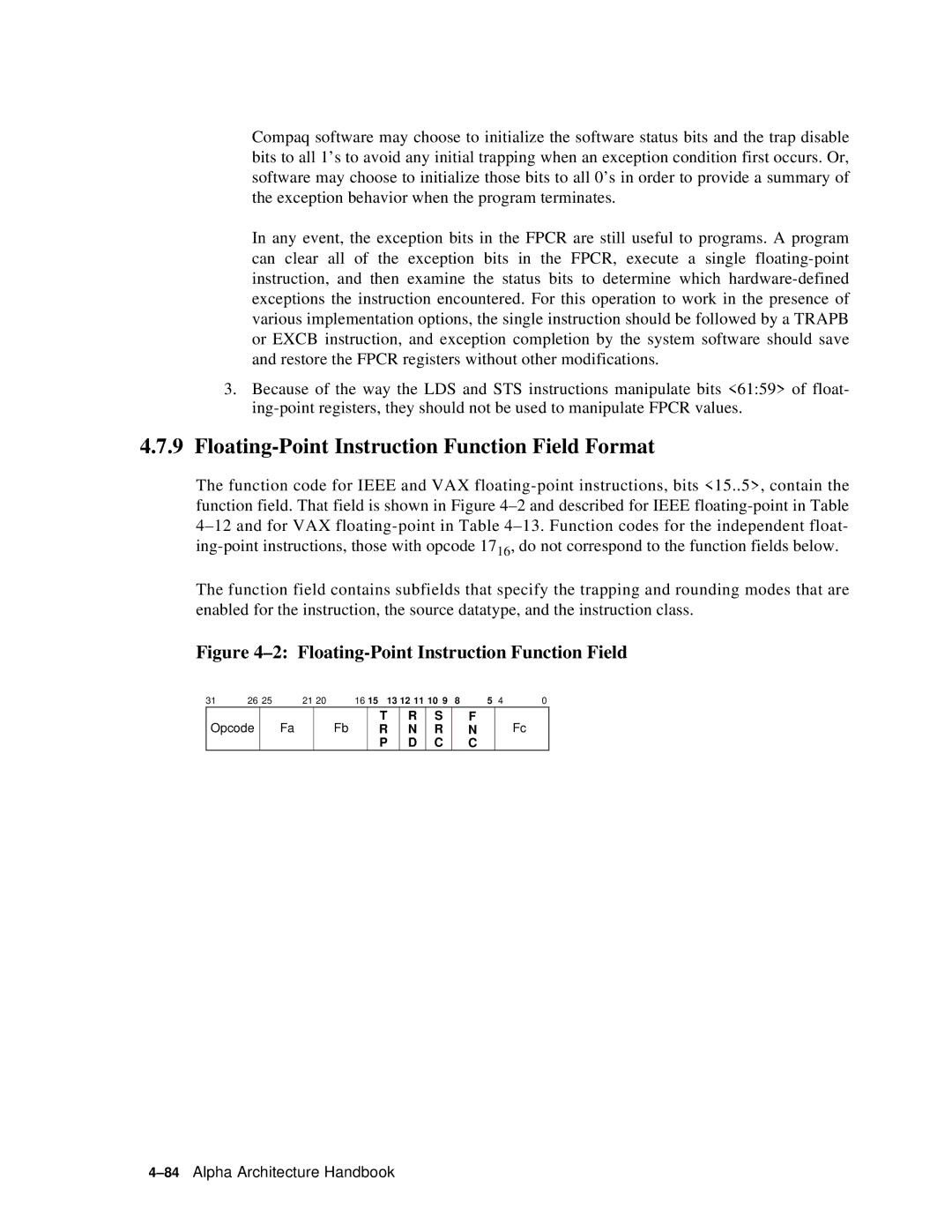

The function code for IEEE and VAX

The function field contains subfields that specify the trapping and rounding modes that are enabled for the instruction, the source datatype, and the instruction class.

Figure 4–2: Floating-Point Instruction Function Field

31 | 26 25 | 21 20 | 16 15 | 13 12 11 10 9 | 8 | 5 | 4 | 0 | |||||

Opcode | Fa |

| Fb |

|

| T | R | S |

| F |

| Fc | |

|

|

| R | N | R |

| N |

| |||||

|

|

|

|

|

|

| P | D | C |

| C |

|

|