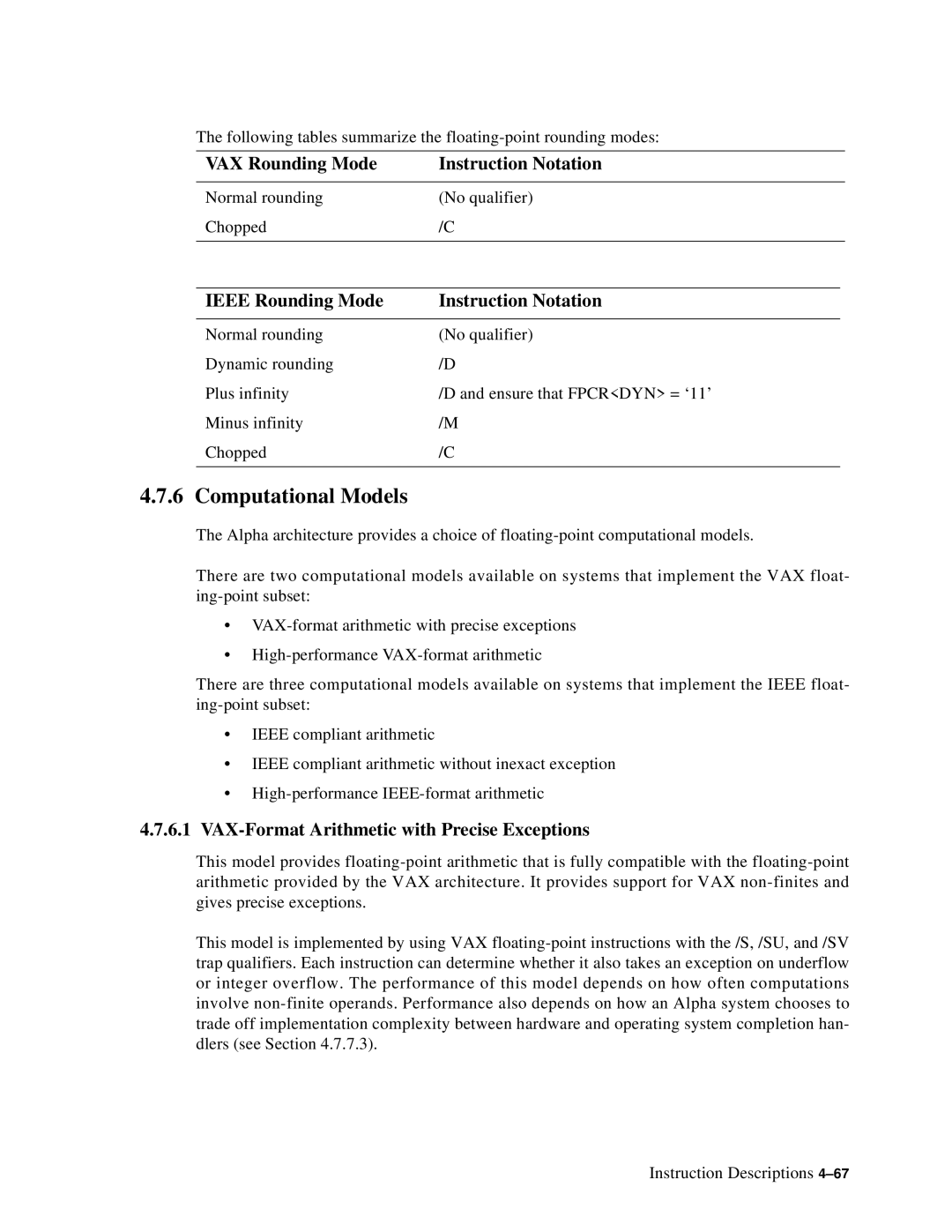

The following tables summarize the

VAX Rounding Mode | Instruction Notation | |

|

|

|

Normal rounding | (No qualifier) | |

Chopped | /C | |

|

|

|

|

|

|

IEEE Rounding Mode | Instruction Notation | |

|

|

|

Normal rounding | (No qualifier) | |

Dynamic rounding | /D | |

Plus infinity | /D and ensure that FPCR<DYN> = ‘11’ | |

Minus infinity | /M | |

Chopped | /C | |

|

|

|

4.7.6 Computational Models

The Alpha architecture provides a choice of

There are two computational models available on systems that implement the VAX float-

•

•

There are three computational models available on systems that implement the IEEE float-

•IEEE compliant arithmetic

•IEEE compliant arithmetic without inexact exception

•

4.7.6.1VAX-Format Arithmetic with Precise Exceptions

This model provides

This model is implemented by using VAX

Instruction Descriptions