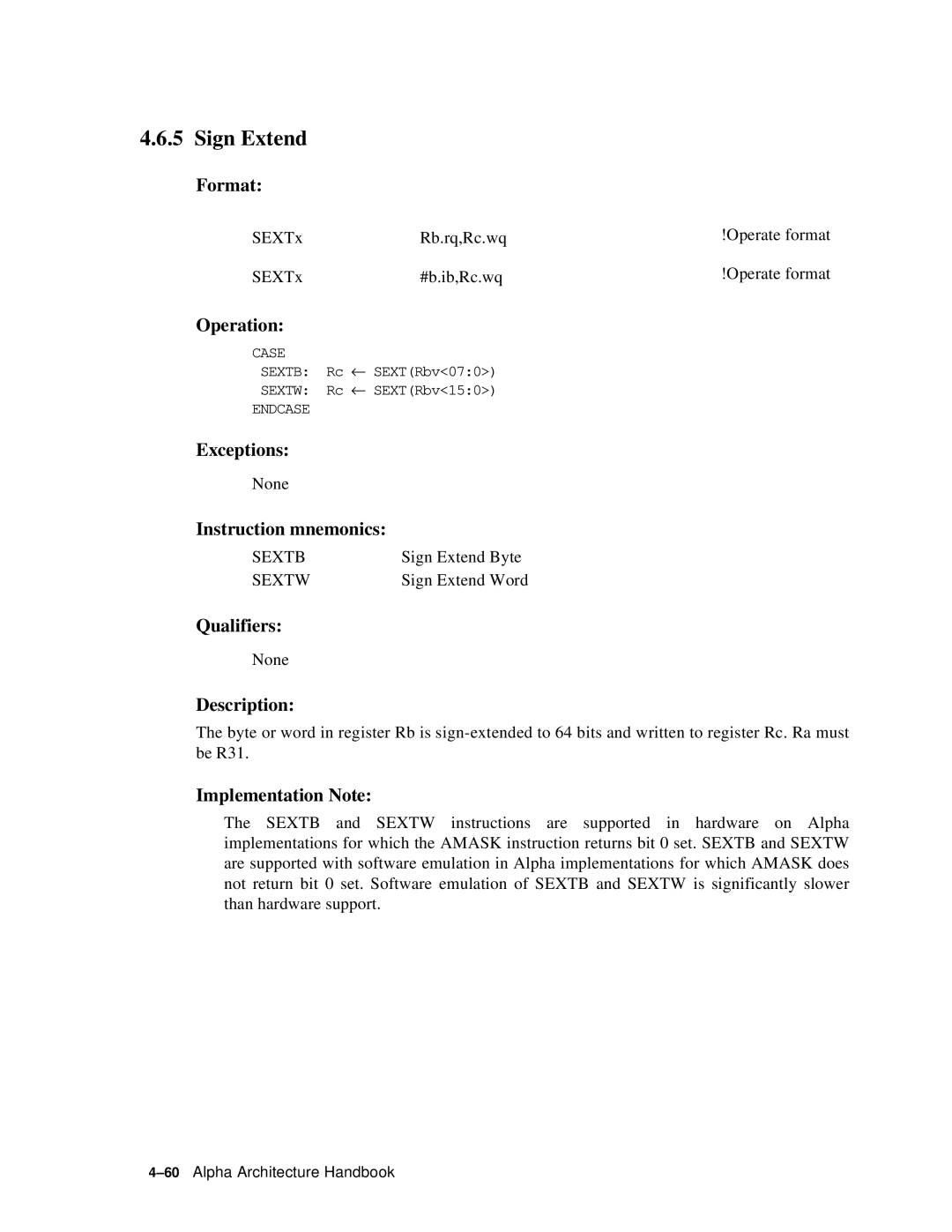

4.6.5 Sign Extend

Format:

SEXTx | Rb.rq,Rc.wq | !Operate format |

SEXTx | #b.ib,Rc.wq | !Operate format |

Operation:

CASE

SEXTB: Rc ← SEXT(Rbv<07:0>)

SEXTW: Rc ← SEXT(Rbv<15:0>)

ENDCASE

Exceptions: |

|

None |

|

Instruction mnemonics: |

|

SEXTB | Sign Extend Byte |

SEXTW | Sign Extend Word |

Qualifiers: |

|

None |

|

Description:

The byte or word in register Rb is

Implementation Note:

The SEXTB and SEXTW instructions are supported in hardware on Alpha implementations for which the AMASK instruction returns bit 0 set. SEXTB and SEXTW are supported with software emulation in Alpha implementations for which AMASK does not return bit 0 set. Software emulation of SEXTB and SEXTW is significantly slower than hardware support.