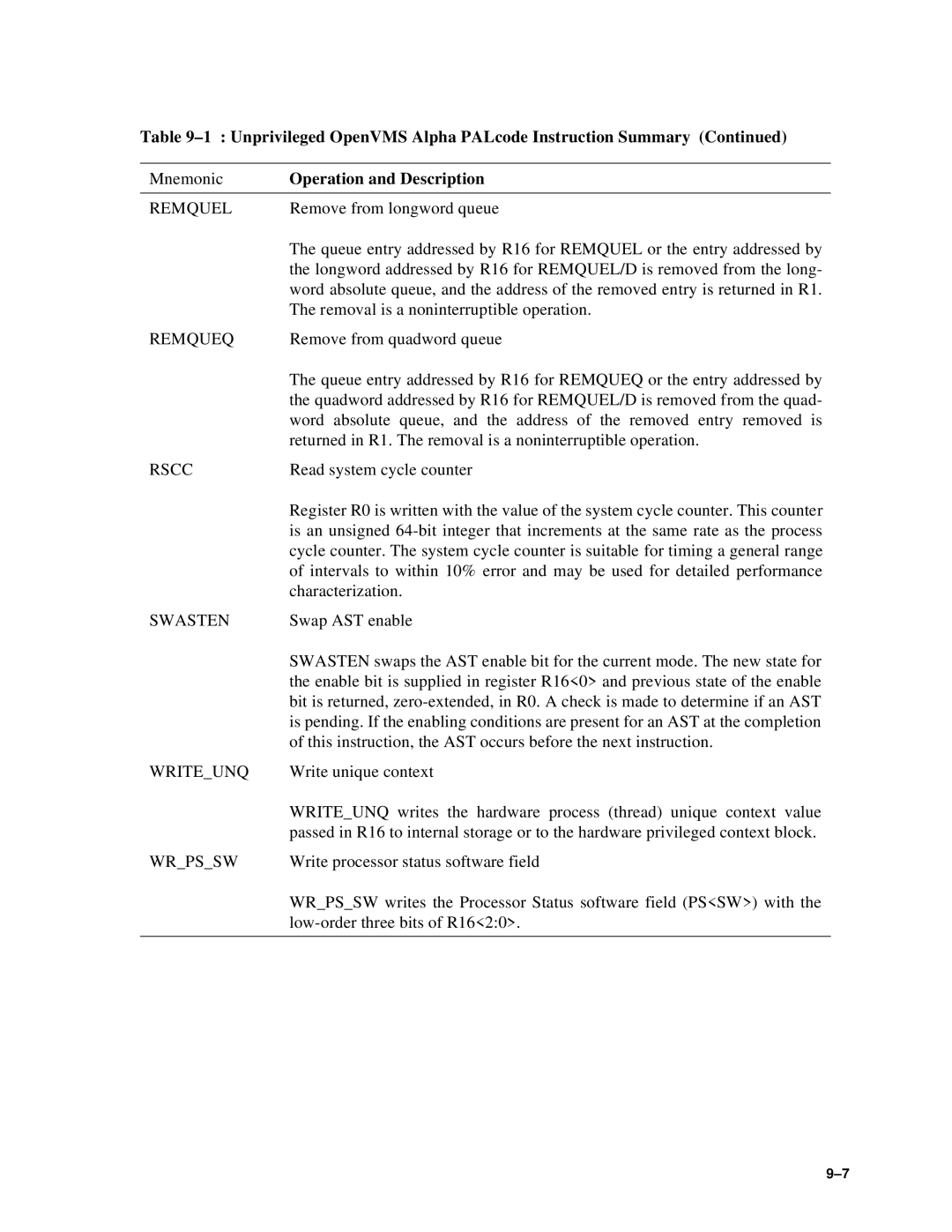

Table

Mnemonic | Operation and Description |

REMQUEL | Remove from longword queue |

| The queue entry addressed by R16 for REMQUEL or the entry addressed by |

| the longword addressed by R16 for REMQUEL/D is removed from the long- |

| word absolute queue, and the address of the removed entry is returned in R1. |

| The removal is a noninterruptible operation. |

REMQUEQ | Remove from quadword queue |

| The queue entry addressed by R16 for REMQUEQ or the entry addressed by |

| the quadword addressed by R16 for REMQUEL/D is removed from the quad- |

| word absolute queue, and the address of the removed entry removed is |

| returned in R1. The removal is a noninterruptible operation. |

RSCC | Read system cycle counter |

| Register R0 is written with the value of the system cycle counter. This counter |

| is an unsigned |

| cycle counter. The system cycle counter is suitable for timing a general range |

| of intervals to within 10% error and may be used for detailed performance |

| characterization. |

SWASTEN | Swap AST enable |

| SWASTEN swaps the AST enable bit for the current mode. The new state for |

| the enable bit is supplied in register R16<0> and previous state of the enable |

| bit is returned, |

| is pending. If the enabling conditions are present for an AST at the completion |

| of this instruction, the AST occurs before the next instruction. |

WRITE_UNQ | Write unique context |

| WRITE_UNQ writes the hardware process (thread) unique context value |

| passed in R16 to internal storage or to the hardware privileged context block. |

WR_PS_SW | Write processor status software field |

| WR_PS_SW writes the Processor Status software field (PS<SW>) with the |

| |

|

|