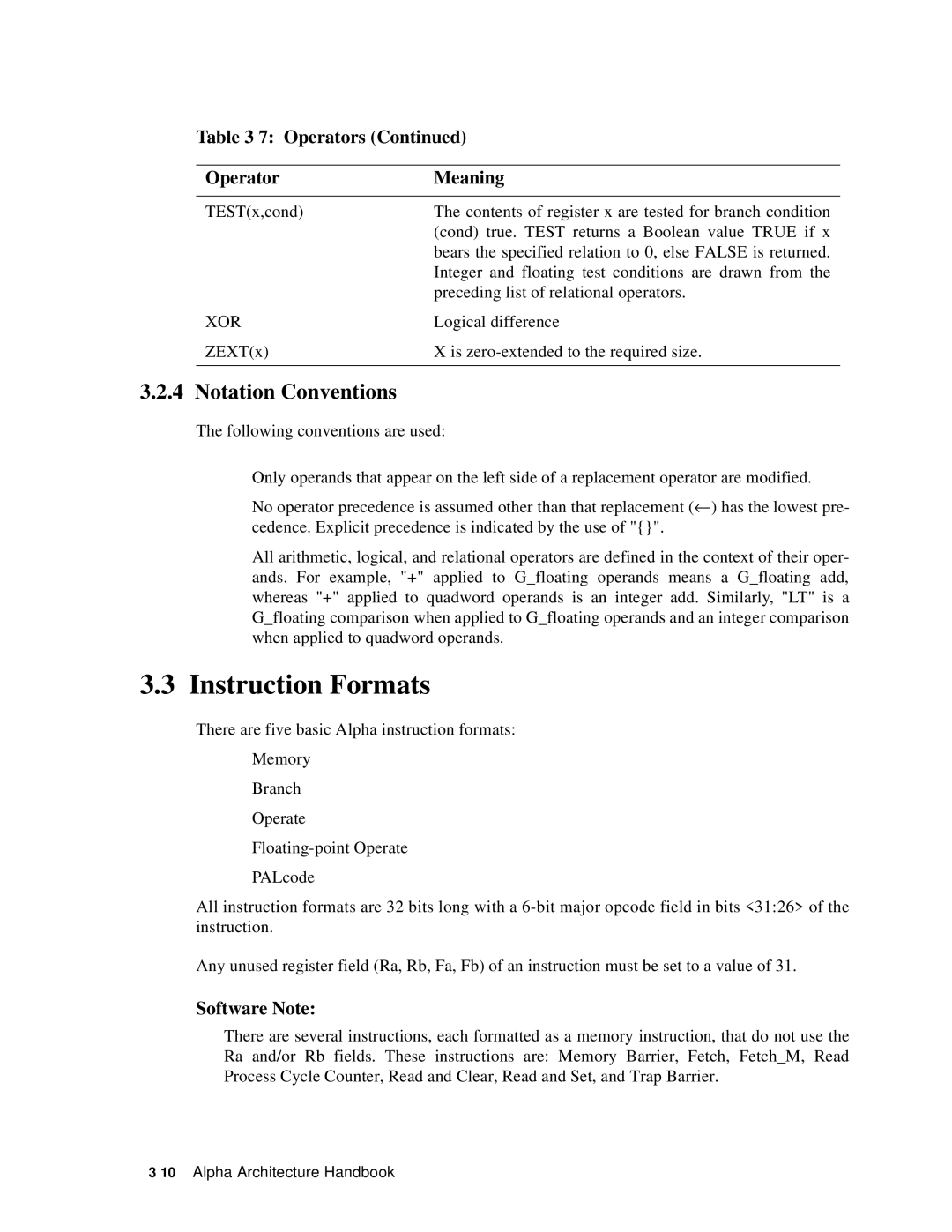

Table 3–7: Operators (Continued)

Operator | Meaning |

|

|

TEST(x,cond) | The contents of register x are tested for branch condition |

| (cond) true. TEST returns a Boolean value TRUE if x |

| bears the specified relation to 0, else FALSE is returned. |

| Integer and floating test conditions are drawn from the |

| preceding list of relational operators. |

XOR | Logical difference |

ZEXT(x) | X is |

|

|

3.2.4 Notation Conventions

The following conventions are used:

•Only operands that appear on the left side of a replacement operator are modified.

•No operator precedence is assumed other than that replacement (←) has the lowest pre- cedence. Explicit precedence is indicated by the use of "{}".

•All arithmetic, logical, and relational operators are defined in the context of their oper- ands. For example, "+" applied to G_floating operands means a G_floating add, whereas "+" applied to quadword operands is an integer add. Similarly, "LT" is a G_floating comparison when applied to G_floating operands and an integer comparison when applied to quadword operands.

3.3Instruction Formats

There are five basic Alpha instruction formats:

•Memory

•Branch

•Operate

•

•PALcode

All instruction formats are 32 bits long with a

Any unused register field (Ra, Rb, Fa, Fb) of an instruction must be set to a value of 31.

Software Note:

There are several instructions, each formatted as a memory instruction, that do not use the Ra and/or Rb fields. These instructions are: Memory Barrier, Fetch, Fetch_M, Read Process Cycle Counter, Read and Clear, Read and Set, and Trap Barrier.