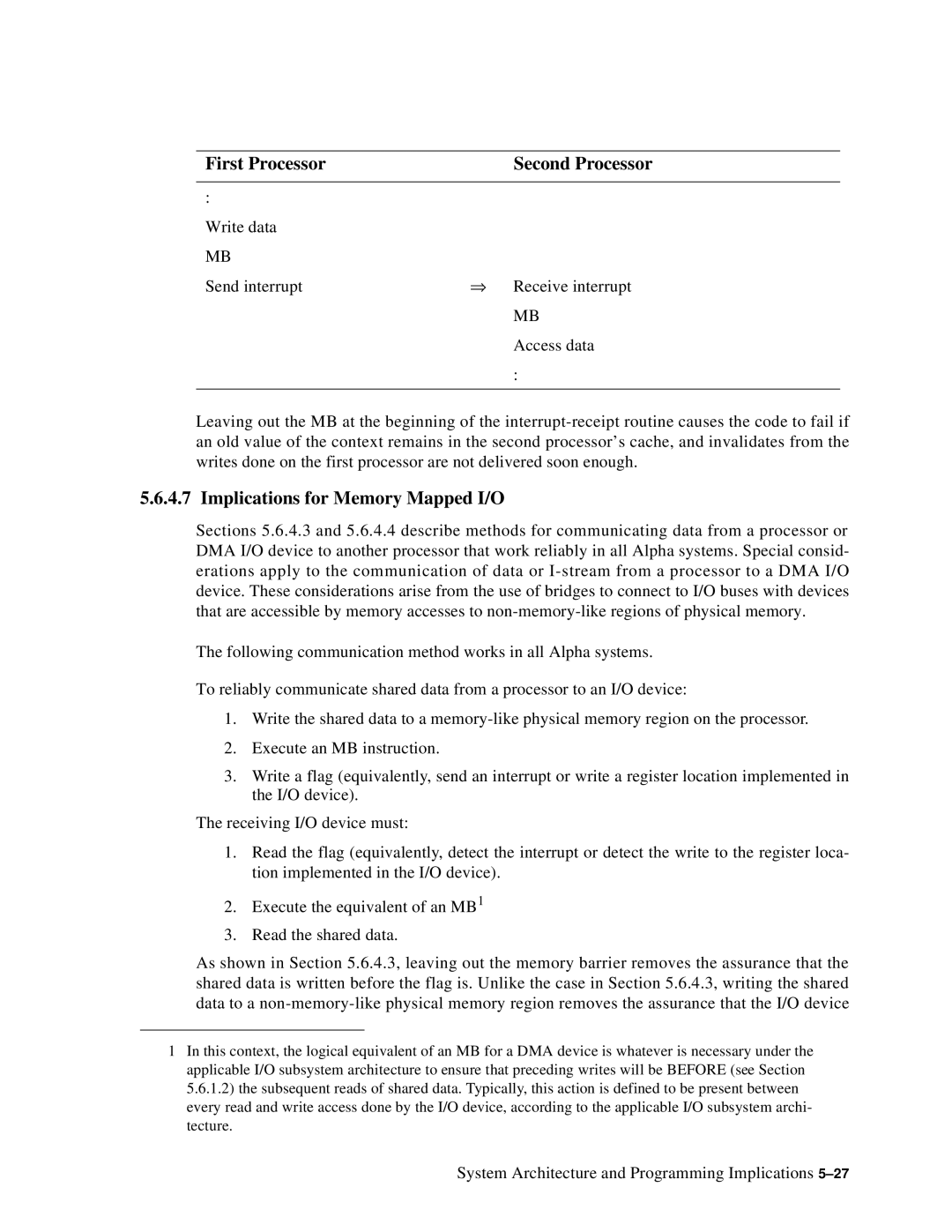

First Processor | Second Processor |

|

|

: |

|

Write data |

|

MB |

|

Send interrupt | ⇒ Receive interrupt |

| MB |

| Access data |

| : |

|

|

Leaving out the MB at the beginning of the

5.6.4.7 Implications for Memory Mapped I/O

Sections 5.6.4.3 and 5.6.4.4 describe methods for communicating data from a processor or DMA I/O device to another processor that work reliably in all Alpha systems. Special consid- erations apply to the communication of data or

The following communication method works in all Alpha systems.

To reliably communicate shared data from a processor to an I/O device:

1.Write the shared data to a

2.Execute an MB instruction.

3.Write a flag (equivalently, send an interrupt or write a register location implemented in the I/O device).

The receiving I/O device must:

1.Read the flag (equivalently, detect the interrupt or detect the write to the register loca- tion implemented in the I/O device).

2.Execute the equivalent of an MB1

3.Read the shared data.

As shown in Section 5.6.4.3, leaving out the memory barrier removes the assurance that the shared data is written before the flag is. Unlike the case in Section 5.6.4.3, writing the shared data to a

1In this context, the logical equivalent of an MB for a DMA device is whatever is necessary under the applicable I/O subsystem architecture to ensure that preceding writes will be BEFORE (see Section 5.6.1.2) the subsequent reads of shared data. Typically, this action is defined to be present between every read and write access done by the I/O device, according to the applicable I/O subsystem archi- tecture.

System Architecture and Programming Implications