9.2 Privileged OpenVMS Alpha Palcode

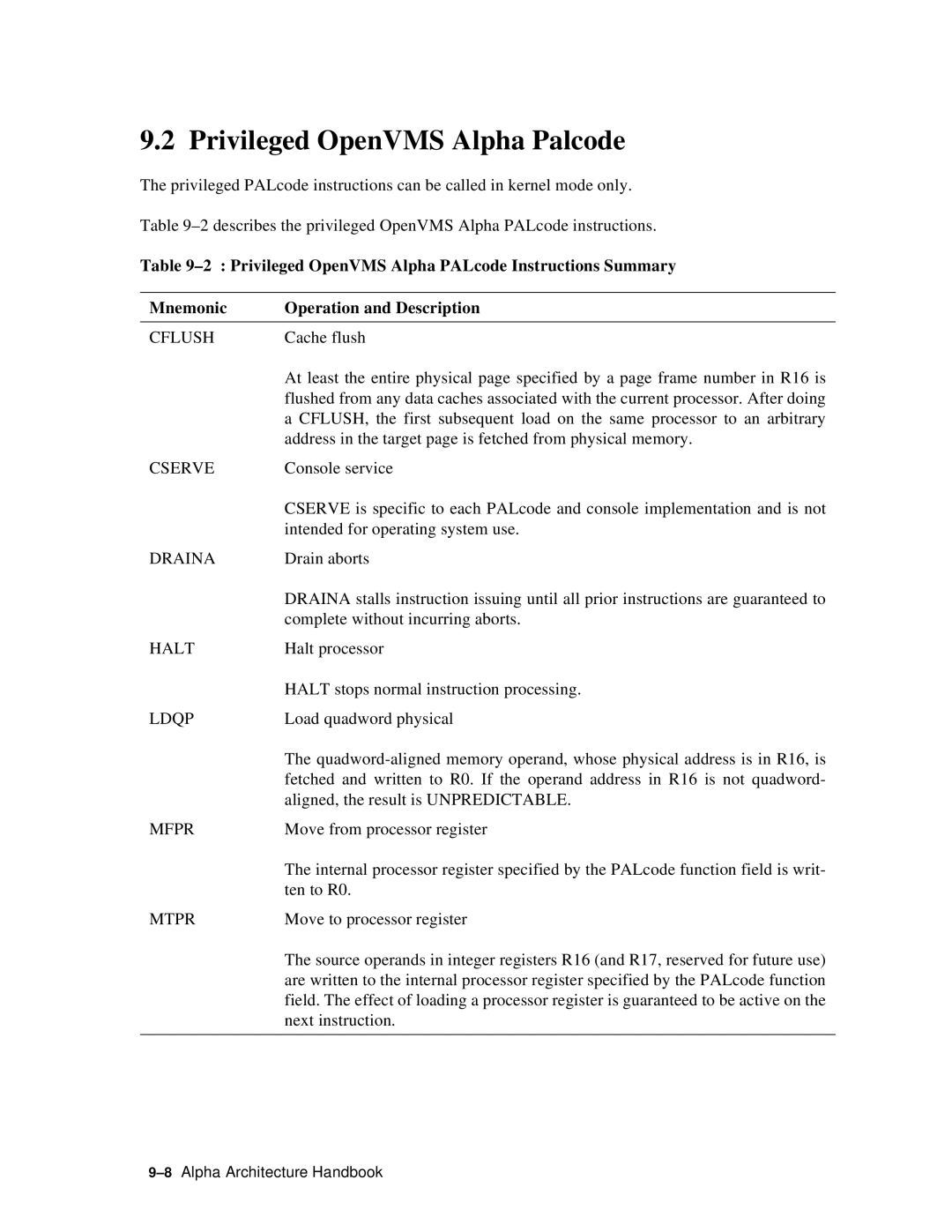

The privileged PALcode instructions can be called in kernel mode only.

Table

Table

Mnemonic | Operation and Description |

CFLUSH | Cache flush |

| At least the entire physical page specified by a page frame number in R16 is |

| flushed from any data caches associated with the current processor. After doing |

| a CFLUSH, the first subsequent load on the same processor to an arbitrary |

| address in the target page is fetched from physical memory. |

CSERVE | Console service |

| CSERVE is specific to each PALcode and console implementation and is not |

| intended for operating system use. |

DRAINA | Drain aborts |

| DRAINA stalls instruction issuing until all prior instructions are guaranteed to |

| complete without incurring aborts. |

HALT | Halt processor |

| HALT stops normal instruction processing. |

LDQP | Load quadword physical |

| The |

| fetched and written to R0. If the operand address in R16 is not quadword- |

| aligned, the result is UNPREDICTABLE. |

MFPR | Move from processor register |

| The internal processor register specified by the PALcode function field is writ- |

| ten to R0. |

MTPR | Move to processor register |

| The source operands in integer registers R16 (and R17, reserved for future use) |

| are written to the internal processor register specified by the PALcode function |

| field. The effect of loading a processor register is guaranteed to be active on the |

| next instruction. |

|

|