NaNs. Signaling NaNs are used to provide values for uninitialized variables and for arithmetic enhancements. Quiet NaNs provide retrospective diagnostic information regarding previous invalid or unavailable data and results. Signaling NaNs signal an invalid operation when they are an operand to an arithmetic instruction, and may generate an arithmetic exception. Quiet NaNs propagate through almost every operation without generating an arithmetic exception.

Arithmetic with the infinities is handled as if the operands were of arbitrarily large magnitude. Negative infinity is less than every finite number; positive infinity is greater than every finite number.

2.2.6.1 S_Floating

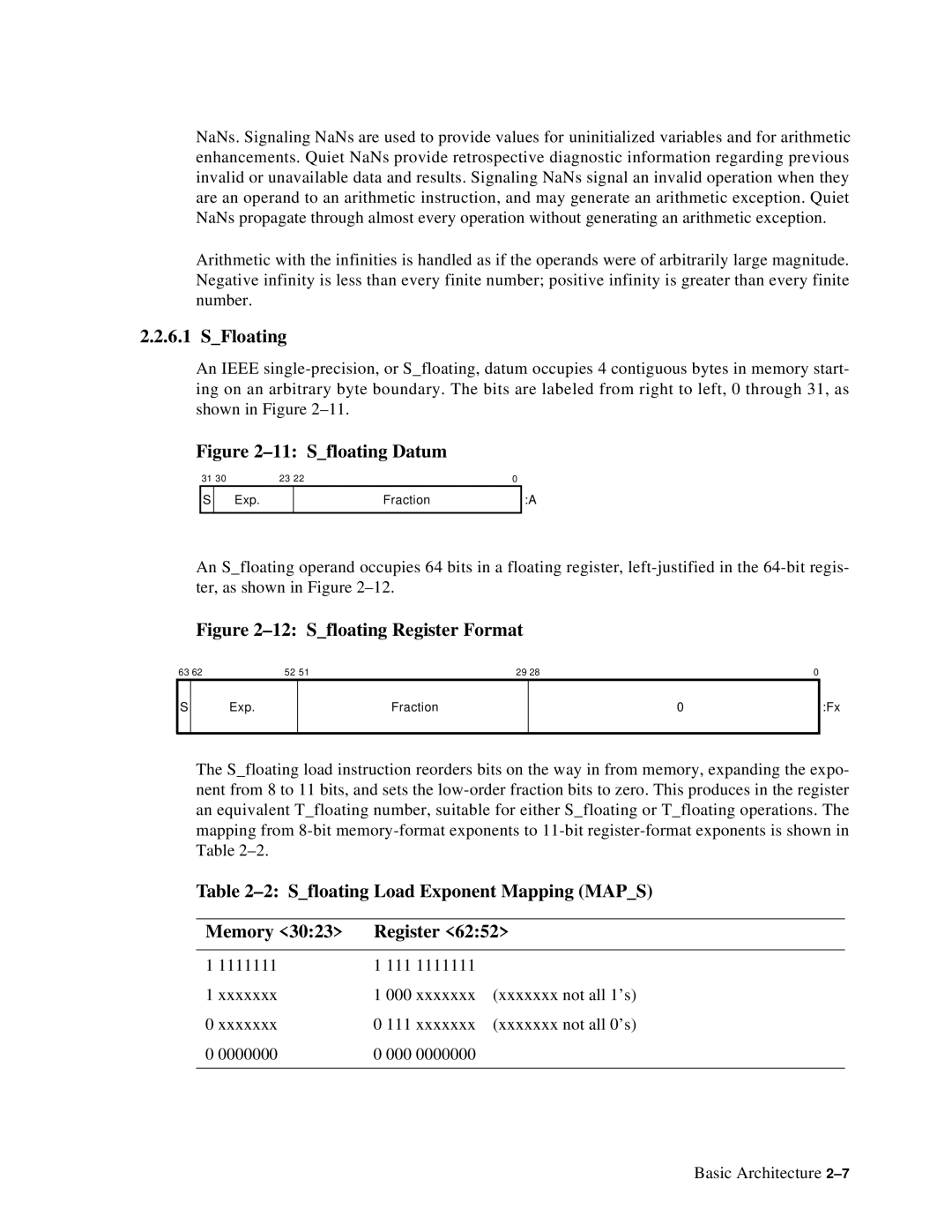

An IEEE

Figure 2–11: S_floating Datum

31 30 | 23 22 | 0 | ||

S |

| Exp. |

| Fraction |

|

|

|

|

|

:A

An S_floating operand occupies 64 bits in a floating register,

Figure 2–12: S_floating Register Format

63 62 | 52 51 | 29 28 | 0 |

S

Exp.

Fraction

0

:Fx

The S_floating load instruction reorders bits on the way in from memory, expanding the expo- nent from 8 to 11 bits, and sets the

Table 2–2: S_floating Load Exponent Mapping (MAP_S)

Memory <30:23> | Register <62:52> |

|

|

1 1111111 | 1 111 1111111 |

1 xxxxxxx | 1 000 xxxxxxx (xxxxxxx not all 1’s) |

0 xxxxxxx | 0 111 xxxxxxx (xxxxxxx not all 0’s) |

0 0000000 | 0 000 0000000 |

|

|

Basic Architecture