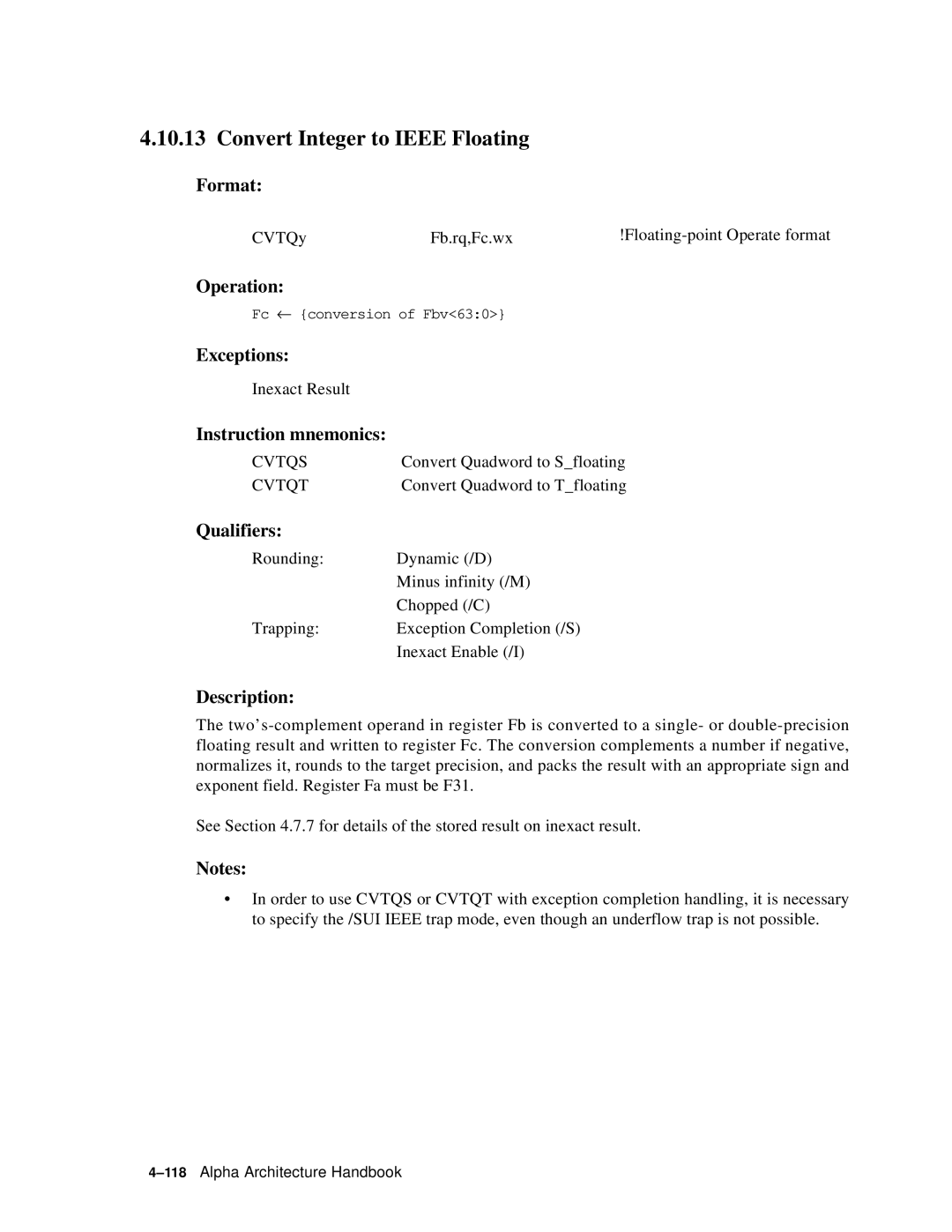

4.10.13 Convert Integer to IEEE Floating

Format:

CVTQy | Fb.rq,Fc.wx |

Operation:

Fc ← {conversion of Fbv<63:0>}

Exceptions:

Inexact Result

Instruction mnemonics:

CVTQS | Convert Quadword to S_floating |

CVTQT | Convert Quadword to T_floating |

Qualifiers:

Rounding: | Dynamic (/D) |

| Minus infinity (/M) |

| Chopped (/C) |

Trapping: | Exception Completion (/S) |

| Inexact Enable (/I) |

Description:

The

See Section 4.7.7 for details of the stored result on inexact result.

Notes:

•In order to use CVTQS or CVTQT with exception completion handling, it is necessary to specify the /SUI IEEE trap mode, even though an underflow trap is not possible.