4.2.5 Store Integer Register Data into Memory Conditional

Format:

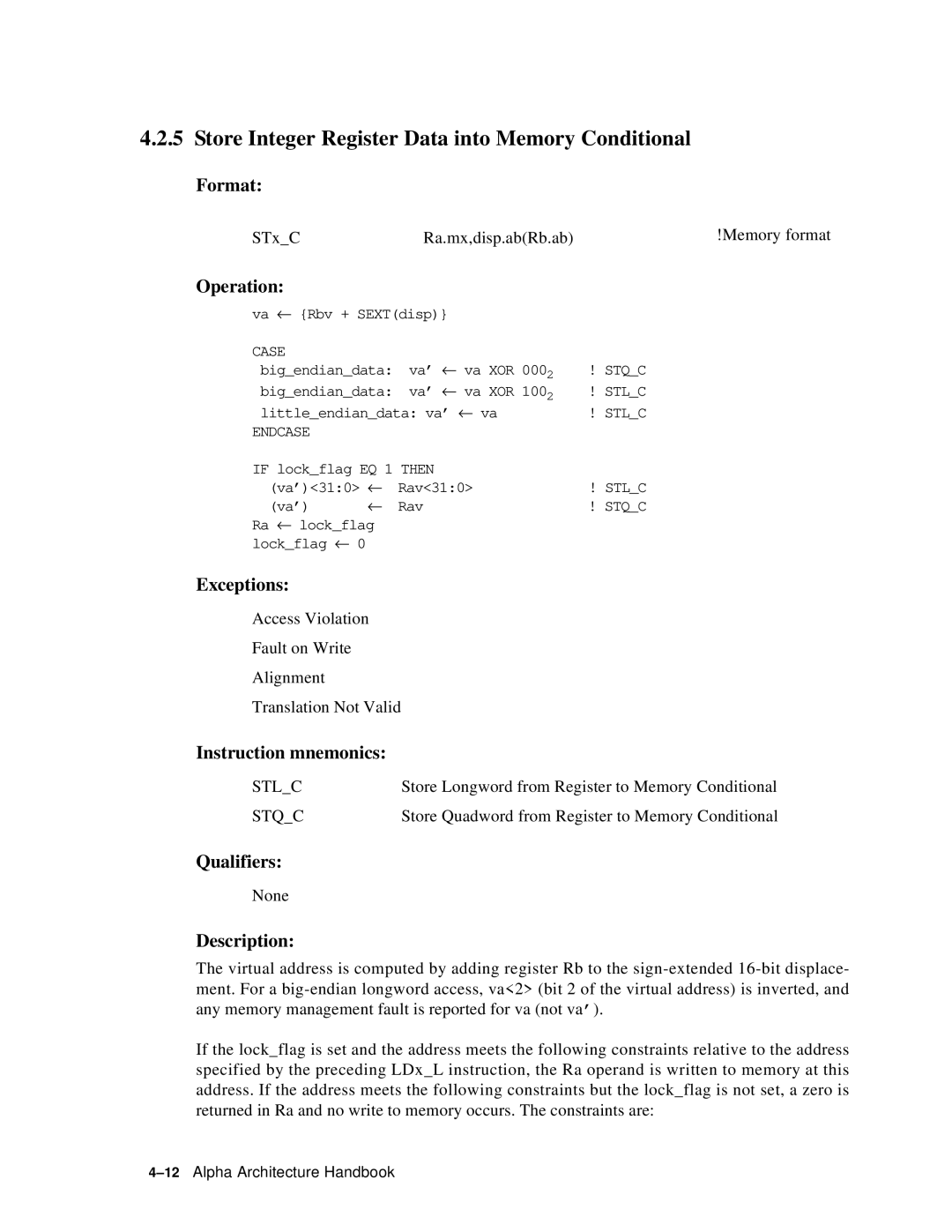

STx_CRa.mx,disp.ab(Rb.ab)!Memory format

Operation:

va ← {Rbv + SEXT(disp)} |

| ||

CASE |

| va’ ← va XOR 0002 |

|

big_endian_data: | ! STQ_C | ||

big_endian_data: | va’ ← va XOR 1002 | ! STL_C | |

little_endian_data: va’ ← va | ! STL_C | ||

ENDCASE |

|

|

|

IF lock_flag EQ 1 THEN |

| ||

(va’)<31:0> ← Rav<31:0> | ! STL_C | ||

(va’) | ← Rav | ! STQ_C | |

Ra ← lock_flag lock_flag ← 0

Exceptions:

Access Violation

Fault on Write

Alignment

Translation Not Valid

Instruction mnemonics:

STL_C | Store Longword from Register to Memory Conditional |

STQ_C | Store Quadword from Register to Memory Conditional |

Qualifiers:

None

Description:

The virtual address is computed by adding register Rb to the

If the lock_flag is set and the address meets the following constraints relative to the address specified by the preceding LDx_L instruction, the Ra operand is written to memory at this address. If the address meets the following constraints but the lock_flag is not set, a zero is returned in Ra and no write to memory occurs. The constraints are: