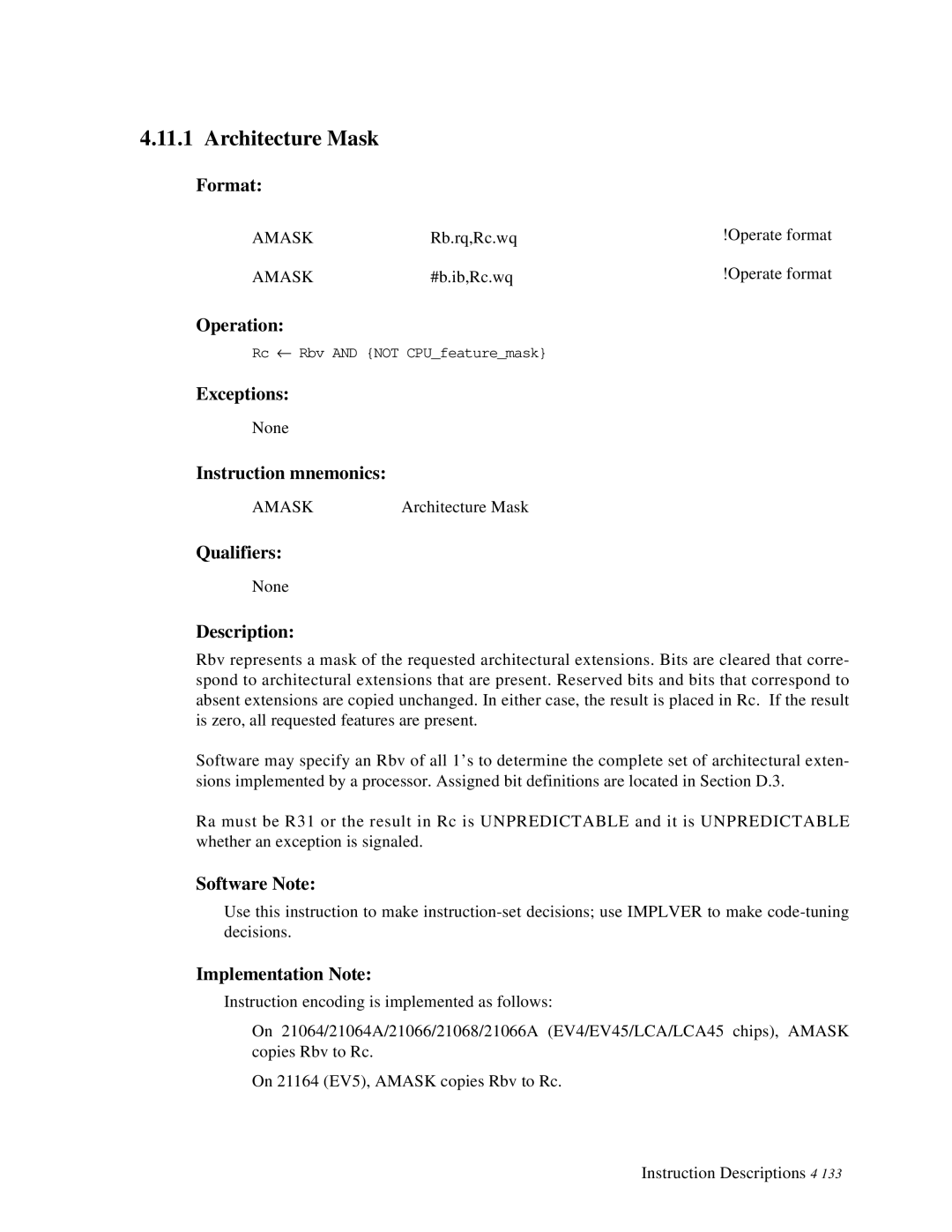

4.11.1 Architecture Mask

Format:

AMASK | Rb.rq,Rc.wq | !Operate format |

AMASK | #b.ib,Rc.wq | !Operate format |

Operation:

Rc ← Rbv AND {NOT CPU_feature_mask}

Exceptions:

None

Instruction mnemonics:

AMASK | Architecture Mask |

Qualifiers:

None

Description:

Rbv represents a mask of the requested architectural extensions. Bits are cleared that corre- spond to architectural extensions that are present. Reserved bits and bits that correspond to absent extensions are copied unchanged. In either case, the result is placed in Rc. If the result is zero, all requested features are present.

Software may specify an Rbv of all 1’s to determine the complete set of architectural exten- sions implemented by a processor. Assigned bit definitions are located in Section D.3.

Ra must be R31 or the result in Rc is UNPREDICTABLE and it is UNPREDICTABLE whether an exception is signaled.

Software Note:

Use this instruction to make

Implementation Note:

Instruction encoding is implemented as follows:

•On 21064/21064A/21066/21068/21066A (EV4/EV45/LCA/LCA45 chips), AMASK copies Rbv to Rc.

•On 21164 (EV5), AMASK copies Rbv to Rc.

Instruction Descriptions