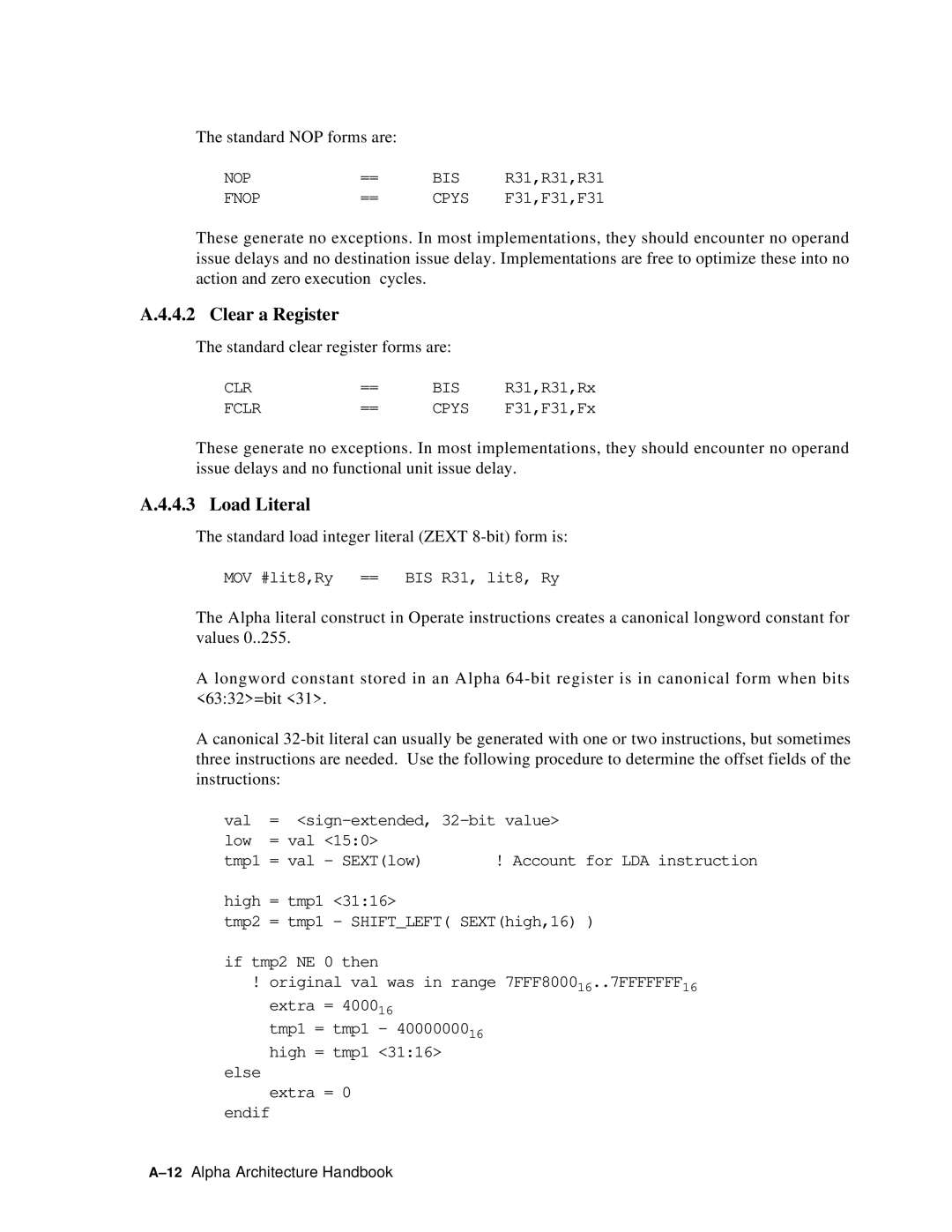

The standard NOP forms are:

NOP | == | BIS | R31,R31,R31 |

FNOP | == | CPYS | F31,F31,F31 |

These generate no exceptions. In most implementations, they should encounter no operand issue delays and no destination issue delay. Implementations are free to optimize these into no action and zero execution cycles.

A.4.4.2 Clear a Register

The standard clear register forms are:

CLR | == | BIS | R31,R31,Rx |

FCLR | == | CPYS | F31,F31,Fx |

These generate no exceptions. In most implementations, they should encounter no operand issue delays and no functional unit issue delay.

A.4.4.3 Load Literal

The standard load integer literal (ZEXT

MOV #lit8,Ry == BIS R31, lit8, Ry

The Alpha literal construct in Operate instructions creates a canonical longword constant for values 0..255.

A longword constant stored in an Alpha

A canonical

val | = | |

low | = val <15:0> |

|

tmp1 | = val - SEXT(low) | ! Account for LDA instruction |

high | = tmp1 <31:16> |

|

tmp2 | = tmp1 - SHIFT_LEFT( SEXT(high,16) ) | |

if tmp2 NE 0 then

!original val was in range 7FFF800016..7FFFFFFF16 extra = 400016

tmp1 = tmp1 - 4000000016

high = tmp1 <31:16>

else

extra = 0 endif