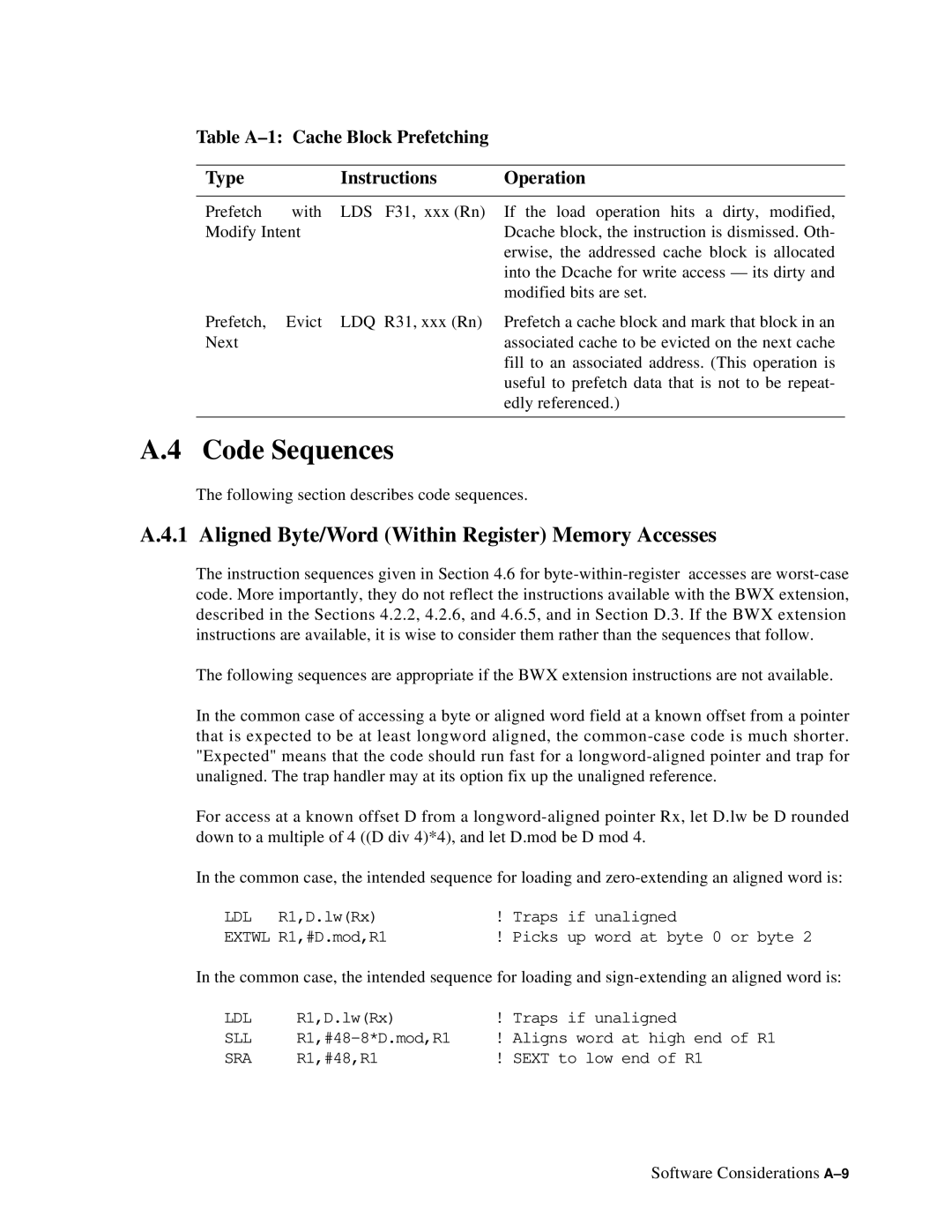

Table

Type |

| Instructions | Operation | |

|

|

|

|

|

Prefetch | with | LDS | F31, xxx (Rn) | If the load operation hits a dirty, modified, |

Modify Intent |

|

| Dcache block, the instruction is dismissed. Oth- | |

|

|

|

| erwise, the addressed cache block is allocated |

|

|

|

| into the Dcache for write access — its dirty and |

|

|

|

| modified bits are set. |

Prefetch, | Evict | LDQ | R31, xxx (Rn) | Prefetch a cache block and mark that block in an |

Next |

|

|

| associated cache to be evicted on the next cache |

|

|

|

| fill to an associated address. (This operation is |

|

|

|

| useful to prefetch data that is not to be repeat- |

|

|

|

| edly referenced.) |

|

|

|

|

|

A.4 Code Sequences

The following section describes code sequences.

A.4.1 Aligned Byte/Word (Within Register) Memory Accesses

The instruction sequences given in Section 4.6 for

The following sequences are appropriate if the BWX extension instructions are not available.

In the common case of accessing a byte or aligned word field at a known offset from a pointer that is expected to be at least longword aligned, the

For access at a known offset D from a

In the common case, the intended sequence for loading and

LDL | R1,D.lw(Rx) | ! | Traps | if | unaligned |

EXTWL | R1,#D.mod,R1 | ! | Picks | up | word at byte 0 or byte 2 |

In the common case, the intended sequence for loading and

LDL | R1,D.lw(Rx) | ! Traps if unaligned |

|

SLL | ! Aligns word at high end of R1 | ||

SRA | R1,#48,R1 | ! SEXT to low end of | R1 |

Software Considerations