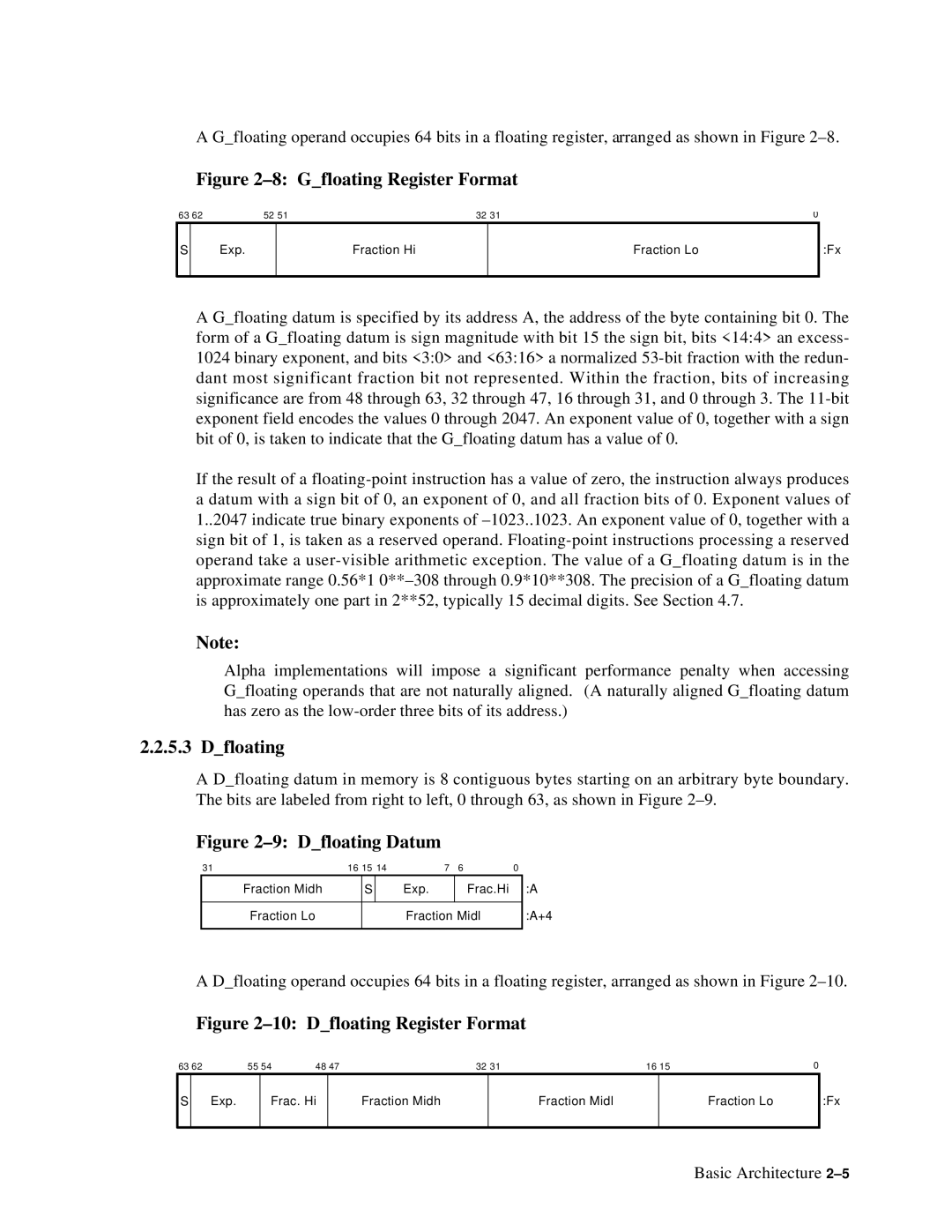

A G_floating operand occupies 64 bits in a floating register, arranged as shown in Figure

Figure 2–8: G_floating Register Format

63 62 | 52 51 | 32 31 | 0 |

S

Exp.

Fraction Hi

Fraction Lo

:Fx

A G_floating datum is specified by its address A, the address of the byte containing bit 0. The form of a G_floating datum is sign magnitude with bit 15 the sign bit, bits <14:4> an excess- 1024 binary exponent, and bits <3:0> and <63:16> a normalized

If the result of a

Note:

Alpha implementations will impose a significant performance penalty when accessing G_floating operands that are not naturally aligned. (A naturally aligned G_floating datum has zero as the

2.2.5.3 D_floating

A D_floating datum in memory is 8 contiguous bytes starting on an arbitrary byte boundary. The bits are labeled from right to left, 0 through 63, as shown in Figure

Figure 2–9: D_floating Datum

31 | 16 15 14 | 7 | 6 | 0 |

| ||

Fraction Midh |

| S |

| Exp. | Frac.Hi |

| :A |

|

|

|

|

|

|

|

|

Fraction Lo |

|

|

| Fraction Midl |

| :A+4 | |

|

|

|

|

|

|

|

|

A D_floating operand occupies 64 bits in a floating register, arranged as shown in Figure

Figure 2–10: D_floating Register Format

63 62 | 55 54 | 48 47 | 32 31 | 16 15 | 0 |

S Exp.

Frac. Hi

Fraction Midh

Fraction Midl

Fraction Lo

:Fx

Basic Architecture