| 2.3 | ||

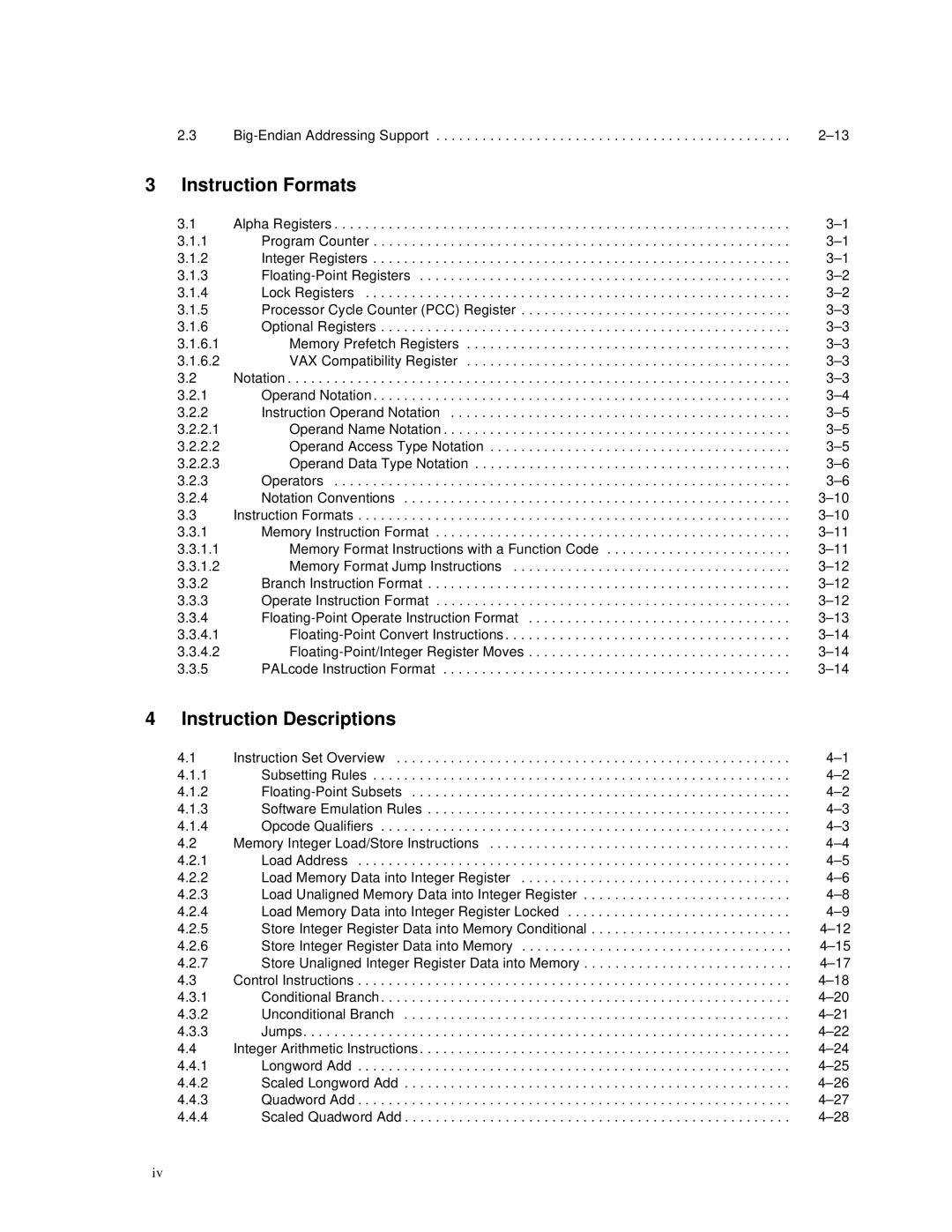

3 | Instruction Formats |

| |

| 3.1 | Alpha Registers | |

| 3.1.1 | Program Counter | |

| 3.1.2 | Integer Registers | |

| 3.1.3 | ||

| 3.1.4 | Lock Registers | |

| 3.1.5 | Processor Cycle Counter (PCC) Register | |

| 3.1.6 | Optional Registers | |

| 3.1.6.1 | Memory Prefetch Registers | |

| 3.1.6.2 | VAX Compatibility Register | |

| 3.2 | Notation | |

| 3.2.1 | Operand Notation | |

| 3.2.2 | Instruction Operand Notation | |

| 3.2.2.1 | Operand Name Notation | |

| 3.2.2.2 | Operand Access Type Notation | |

| 3.2.2.3 | Operand Data Type Notation | |

| 3.2.3 | Operators | |

| 3.2.4 | Notation Conventions | |

| 3.3 | Instruction Formats | |

| 3.3.1 | Memory Instruction Format | |

| 3.3.1.1 | Memory Format Instructions with a Function Code | |

| 3.3.1.2 | Memory Format Jump Instructions | |

| 3.3.2 | Branch Instruction Format | |

| 3.3.3 | Operate Instruction Format | |

| 3.3.4 | ||

| 3.3.4.1 | ||

| 3.3.4.2 | ||

| 3.3.5 | PALcode Instruction Format | |

4 | Instruction Descriptions |

| |

| 4.1 | Instruction Set Overview | |

| 4.1.1 | Subsetting Rules | |

| 4.1.2 | ||

| 4.1.3 | Software Emulation Rules | |

| 4.1.4 | Opcode Qualifiers | |

| 4.2 | Memory Integer Load/Store Instructions | |

| 4.2.1 | Load Address | |

| 4.2.2 | Load Memory Data into Integer Register | |

| 4.2.3 | Load Unaligned Memory Data into Integer Register | |

| 4.2.4 | Load Memory Data into Integer Register Locked | |

| 4.2.5 | Store Integer Register Data into Memory Conditional | |

| 4.2.6 | Store Integer Register Data into Memory | |

| 4.2.7 | Store Unaligned Integer Register Data into Memory | |

| 4.3 | Control Instructions | |

| 4.3.1 | Conditional Branch | |

| 4.3.2 | Unconditional Branch | |

| 4.3.3 | Jumps | |

| 4.4 | Integer Arithmetic Instructions | |

| 4.4.1 | Longword Add | |

| 4.4.2 | Scaled Longword Add | |

| 4.4.3 | Quadword Add | |

| 4.4.4 | Scaled Quadword Add | |

iv