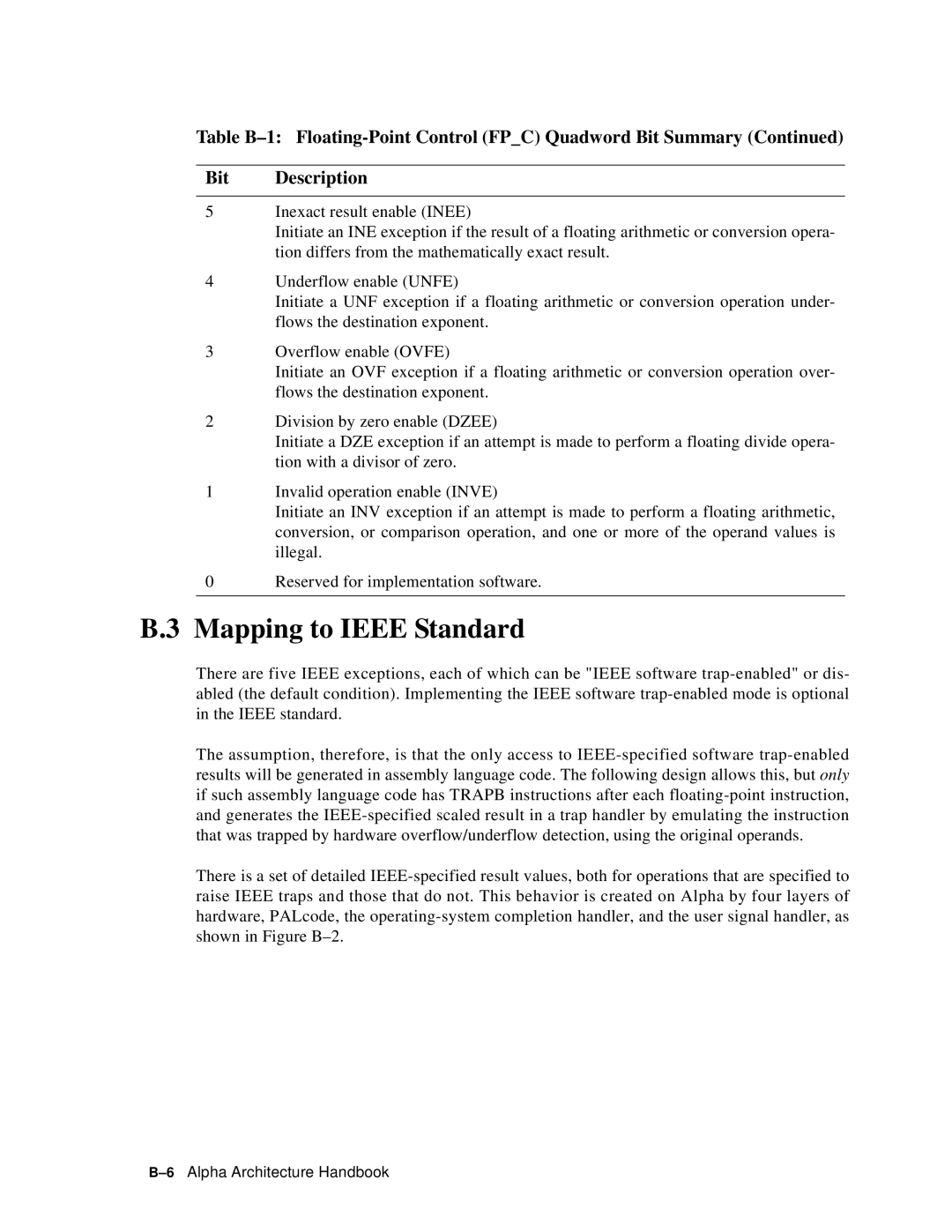

Table

Bit Description

5Inexact result enable (INEE)

Initiate an INE exception if the result of a floating arithmetic or conversion opera- tion differs from the mathematically exact result.

4Underflow enable (UNFE)

Initiate a UNF exception if a floating arithmetic or conversion operation under- flows the destination exponent.

3Overflow enable (OVFE)

Initiate an OVF exception if a floating arithmetic or conversion operation over- flows the destination exponent.

2Division by zero enable (DZEE)

Initiate a DZE exception if an attempt is made to perform a floating divide opera- tion with a divisor of zero.

1Invalid operation enable (INVE)

Initiate an INV exception if an attempt is made to perform a floating arithmetic, conversion, or comparison operation, and one or more of the operand values is illegal.

0 | Reserved for implementation software. |

B.3 Mapping to IEEE Standard

There are five IEEE exceptions, each of which can be "IEEE software

The assumption, therefore, is that the only access to

There is a set of detailed