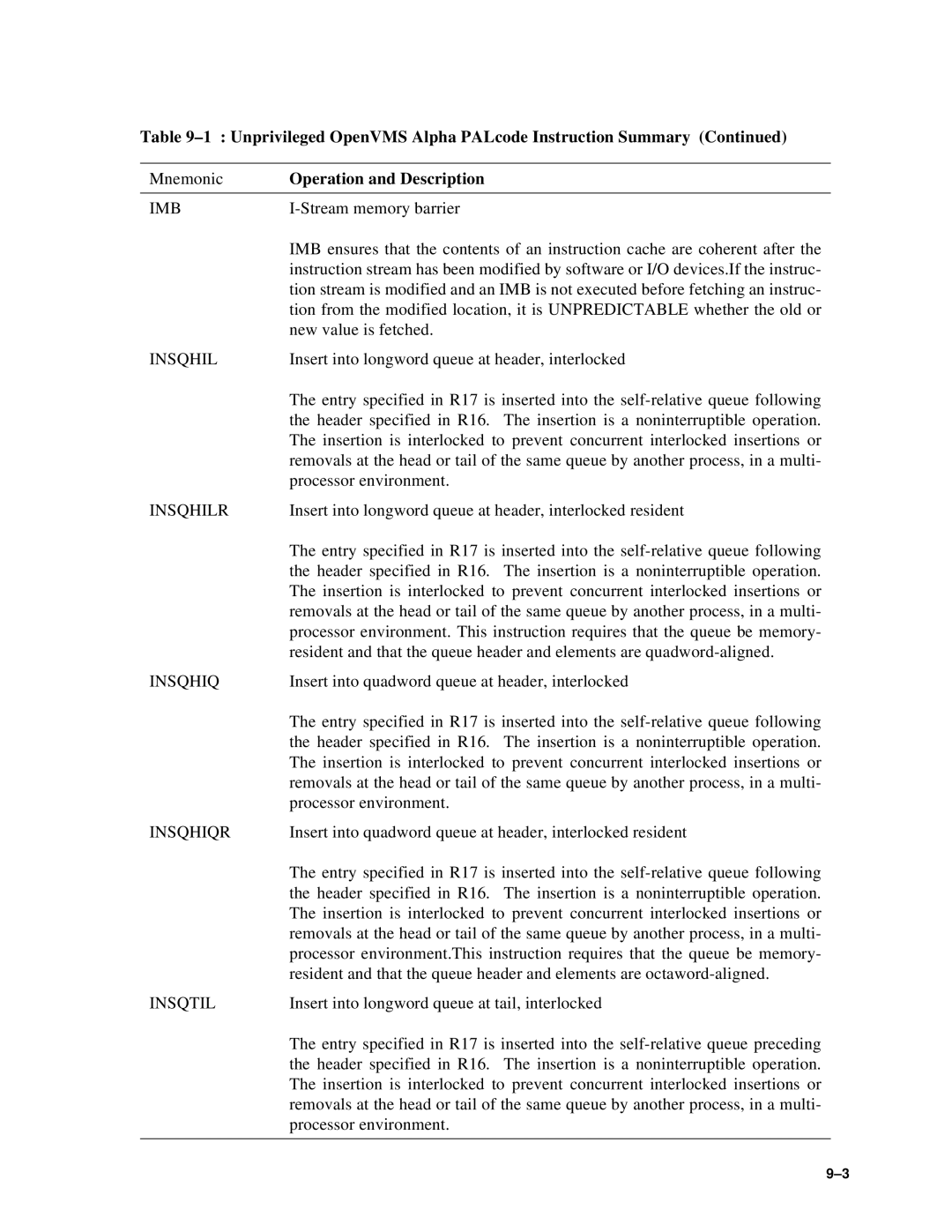

Table

Mnemonic | Operation and Description |

IMB | |

| IMB ensures that the contents of an instruction cache are coherent after the |

| instruction stream has been modified by software or I/O devices.If the instruc- |

| tion stream is modified and an IMB is not executed before fetching an instruc- |

| tion from the modified location, it is UNPREDICTABLE whether the old or |

| new value is fetched. |

INSQHIL | Insert into longword queue at header, interlocked |

| The entry specified in R17 is inserted into the |

| the header specified in R16. The insertion is a noninterruptible operation. |

| The insertion is interlocked to prevent concurrent interlocked insertions or |

| removals at the head or tail of the same queue by another process, in a multi- |

| processor environment. |

INSQHILR | Insert into longword queue at header, interlocked resident |

| The entry specified in R17 is inserted into the |

| the header specified in R16. The insertion is a noninterruptible operation. |

| The insertion is interlocked to prevent concurrent interlocked insertions or |

| removals at the head or tail of the same queue by another process, in a multi- |

| processor environment. This instruction requires that the queue be memory- |

| resident and that the queue header and elements are |

INSQHIQ | Insert into quadword queue at header, interlocked |

| The entry specified in R17 is inserted into the |

| the header specified in R16. The insertion is a noninterruptible operation. |

| The insertion is interlocked to prevent concurrent interlocked insertions or |

| removals at the head or tail of the same queue by another process, in a multi- |

| processor environment. |

INSQHIQR | Insert into quadword queue at header, interlocked resident |

| The entry specified in R17 is inserted into the |

| the header specified in R16. The insertion is a noninterruptible operation. |

| The insertion is interlocked to prevent concurrent interlocked insertions or |

| removals at the head or tail of the same queue by another process, in a multi- |

| processor environment.This instruction requires that the queue be memory- |

| resident and that the queue header and elements are |

INSQTIL | Insert into longword queue at tail, interlocked |

| The entry specified in R17 is inserted into the |

| the header specified in R16. The insertion is a noninterruptible operation. |

| The insertion is interlocked to prevent concurrent interlocked insertions or |

| removals at the head or tail of the same queue by another process, in a multi- |

| processor environment. |

|

|