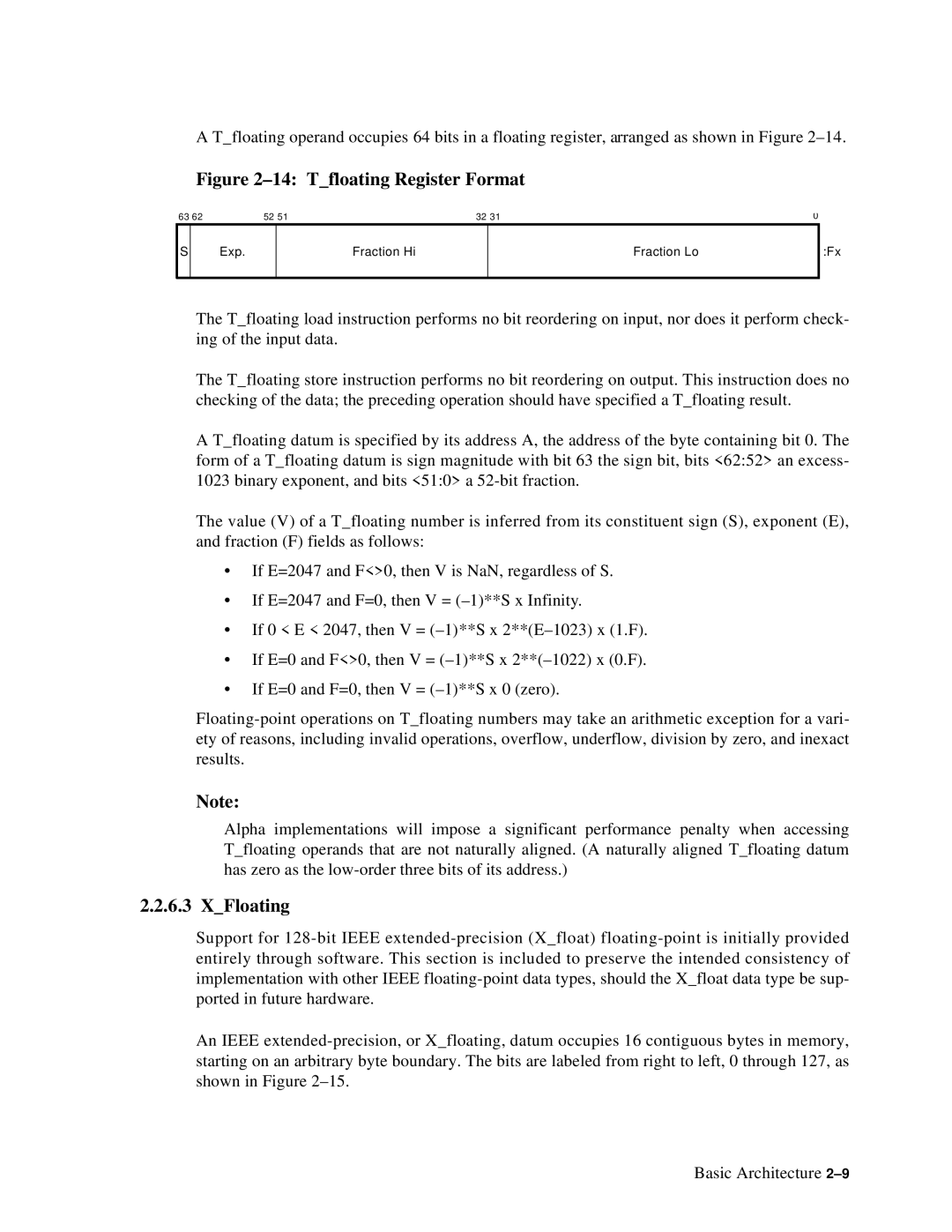

A T_floating operand occupies 64 bits in a floating register, arranged as shown in Figure

Figure 2–14: T_floating Register Format

63 62 | 52 51 | 32 31 | 0 |

S

Exp.

Fraction Hi

Fraction Lo

:Fx

The T_floating load instruction performs no bit reordering on input, nor does it perform check- ing of the input data.

The T_floating store instruction performs no bit reordering on output. This instruction does no checking of the data; the preceding operation should have specified a T_floating result.

A T_floating datum is specified by its address A, the address of the byte containing bit 0. The form of a T_floating datum is sign magnitude with bit 63 the sign bit, bits <62:52> an excess- 1023 binary exponent, and bits <51:0> a

The value (V) of a T_floating number is inferred from its constituent sign (S), exponent (E), and fraction (F) fields as follows:

•If E=2047 and F<>0, then V is NaN, regardless of S.

•If E=2047 and F=0, then V =

•If 0 < E < 2047, then V =

•If E=0 and F<>0, then V =

•If E=0 and F=0, then V =

Note:

Alpha implementations will impose a significant performance penalty when accessing T_floating operands that are not naturally aligned. (A naturally aligned T_floating datum has zero as the

2.2.6.3 X_Floating

Support for

An IEEE

Basic Architecture