4.10 Floating-Point Operate Format Instructions

The

The

Each instruction specifies the source and destination formats of the values, as well as the rounding mode and trapping mode to be used. These instructions use the

The FIX extension to the architecture provides the FTOIx, ITOFx, and SQRTx instructions. Alpha processors for which the AMASK instruction returns bit 1 set implement these instructions. Those processors for which AMASK does not return bit 1 set can take an Illegal Instruction trap, and software can emulate their function, if required. AMASK is described in Sections 4.11.1 and D.3.

The

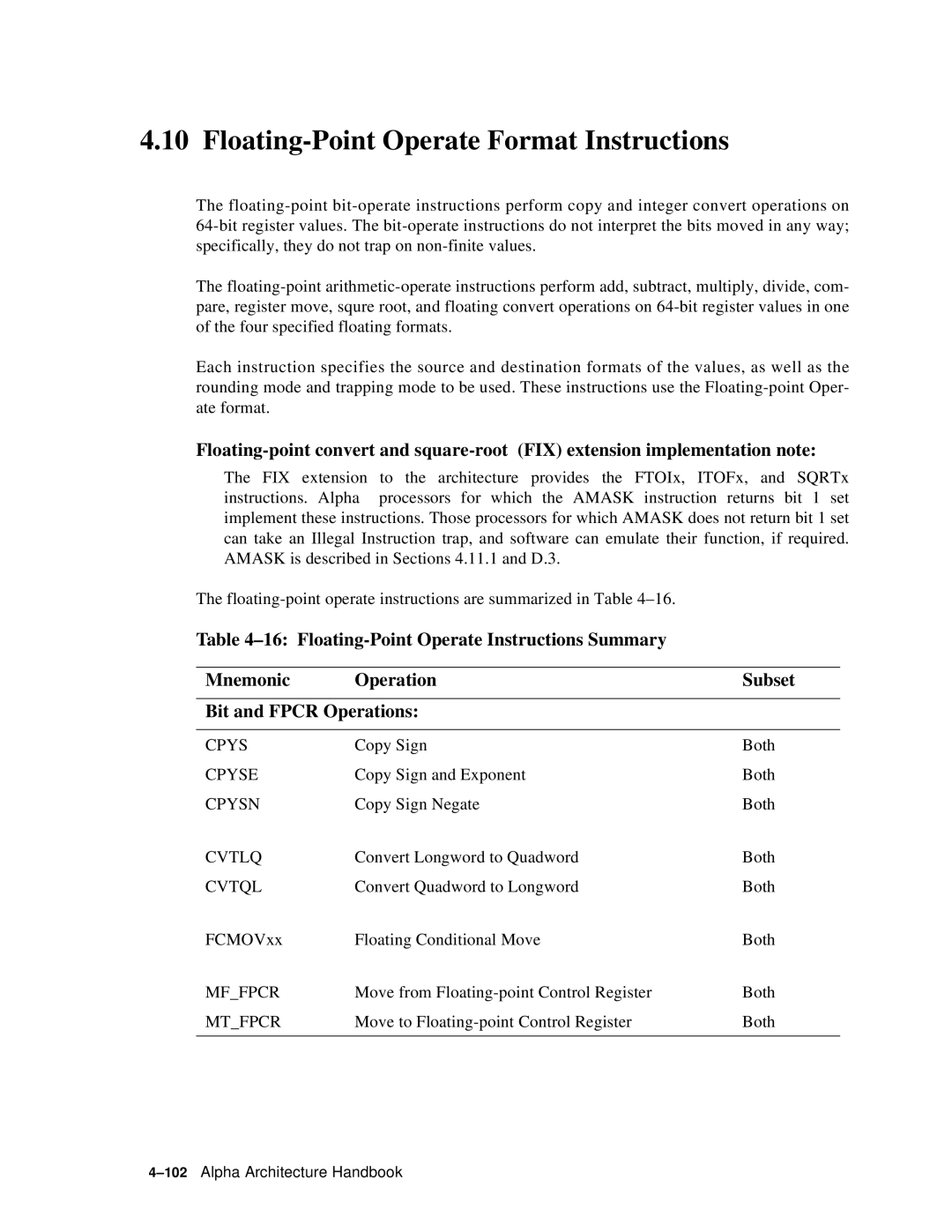

Table

Mnemonic | Operation | Subset |

|

| |

Bit and FPCR Operations: |

| |

|

|

|

CPYS | Copy Sign | Both |

CPYSE | Copy Sign and Exponent | Both |

CPYSN | Copy Sign Negate | Both |

CVTLQ | Convert Longword to Quadword | Both |

CVTQL | Convert Quadword to Longword | Both |

FCMOVxx | Floating Conditional Move | Both |

MF_FPCR | Move from | Both |

MT_FPCR | Move to | Both |

|

|

|