•Traps are imprecise, and it is not always possible to determine which instruction trig- gered a trap or the operands of that instruction.

•An underflow trap produces a zero.

•A conversion to integer trap with an integer overflow produces the

•The result of any other operation that traps is UNPREDICTABLE.

When /SU or /SV mode is specified:

•Arithmetic is performed on all IEEE values, both finite and

•Alpha systems support all IEEE features except inexact exception (which requires /SUI or /SVI):

–The IEEE standard specifies a default where exceptions do not fault or trap.In com- bination with the FPCR, this mode allows disabling exceptions and producing IEEE compliant nontrapping results. See Sections 4.7.7.10 and 4.7.7.11.

–Each Alpha operating system provides a way to optionally signal IEEE floating- point exceptions. This mode enables the IEEE status flags that keep a record of each exception that is encountered. An Alpha operating system uses the IEEE float-

•Exceptions signaled in this mode are precise and an application can locate the instruc- tion that caused the exception, along with its operand values. See Section 4.7.7.3.

When /SUI or /SVI mode is specified:

•Arithmetic is performed on all IEEE values, both finite and

•Inexact exceptions are supported, along with all the other IEEE features supported by the /SU or /SV mode.

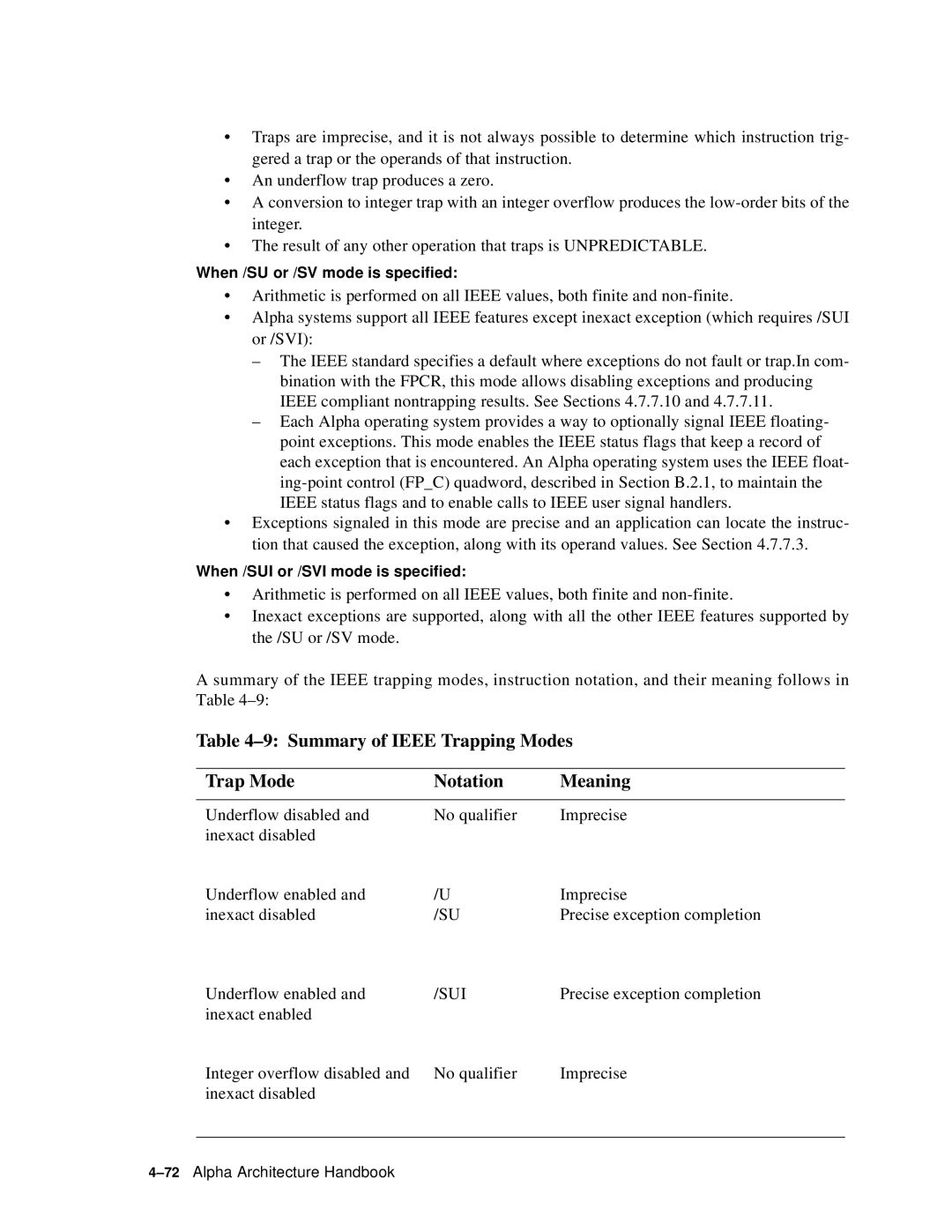

A summary of the IEEE trapping modes, instruction notation, and their meaning follows in Table

Table 4–9: Summary of IEEE Trapping Modes

Trap Mode | Notation | Meaning |

|

|

|

Underflow disabled and | No qualifier | Imprecise |

inexact disabled |

|

|

Underflow enabled and | /U | Imprecise |

inexact disabled | /SU | Precise exception completion |

Underflow enabled and | /SUI | Precise exception completion |

inexact enabled |

|

|

Integer overflow disabled and | No qualifier | Imprecise |

inexact disabled |

|

|